书名:新型超陡亚阈值斜率晶体管

ISBN:978-7-115-68013-6

本书由人民邮电出版社发行数字版。版权所有,侵权必究。

您购买的人民邮电出版社电子书仅供您个人使用,未经授权,不得以任何方式复制和传播本书内容。

我们愿意相信读者具有这样的良知和觉悟,与我们共同保护知识产权。

如果购买者有侵权行为,我们可能对该用户实施包括但不限于关闭该帐号等维权措施,并可能追究法律责任。

著 蒋春生 许 军 化麒麟

责任编辑 顾慧毅

人民邮电出版社出版发行 北京市丰台区成寿寺路11号

邮编 100164 电子邮件 315@ptpress.com.cn

网址 http://www.ptpress.com.cn

读者服务热线:(010)81055410

反盗版热线:(010)81055315

超陡亚阈值斜率晶体管是后摩尔时代实现低功耗集成电路的主要技术途径。本书围绕超陡亚阈值斜率晶体管的工作原理、电学特性、紧凑建模及实验制备等方面展开介绍,共7章。第1章概述晶体管与集成电路的发展历史、超陡亚阈值斜率晶体管的研究现状和面临的挑战等。第2章介绍环栅负电容隧穿场效应晶体管的解析模型和工作原理等。第3章重点分析硅基多栅负电容场效应晶体管的解析模型和应用等。第4章讨论2D沟道材料负电容场效应晶体管的实验制备、解析建模等。第5章研究负电容氧化物薄膜晶体管的实验制备及工艺优化。第6章提出一种新型负电容无结型场效应晶体管,深入分析该器件的数值仿真研究和解析模型。第7章详细探讨基于原子阈值开关的混合场效应晶体管的实验制备、电学特性、工作机理及应用。

本书的研究成果不仅为超陡亚阈值斜率晶体管的设计和优化提供了系统性的理论依据,也为低功耗集成电路的发展提供了新的技术思路。本书可供从事低功耗集成电路设计与研究的学者、工程师及相关领域的学生参考。

主任:郝跃,西安电子科技大学教授,中国科学院院士

委员(以姓氏拼音排序):

陈建平 上海交通大学

陈景东 西北工业大学

高会军 哈尔滨工业大学

黄庆安 东南大学

纪越峰 北京邮电大学

季向阳 清华大学

吕卫锋 北京航空航天大学

辛建国 北京理工大学

尹建伟 浙江大学

张怀武 电子科技大学

张 兴 北京大学

庄钊文 国防科技大学

秘书长:张春福,西安电子科技大学教授

主任:陈英,中国电子学会副理事长兼秘书长、总部党委书记

张立科,中国工信出版传媒集团有限责任公司副总经理

委员:曹玉红,张春福,王威,荆博,韦毅,贺瑞君,郭家,林舒媛,

邓昱洲,顾慧毅,龚昕岳

电子信息科学与技术是现代信息社会的基石,也是科技革命和产业变革的关键,其发展日新月异。近年来,我国电子信息科技和相关产业蓬勃发展,为社会、经济发展和向智能社会升级提供了强有力的支撑,但同时我国仍迫切需要进一步完善电子信息科技自主创新体系,切实提升原始创新能力,努力实现更多“从 0到1”的原创性、基础性研究突破。《中华人民共和国国民经济和社会发展第十四个五年规划和2035年远景目标纲要》明确提出,要发展壮大新一代信息技术等战略性新兴产业。面向未来,我们亟待在电子信息前沿领域重点发展方向上进行系统化建设,持续推出一批能代表学科前沿与发展趋势,展现关键技术突破的有创见、有影响的高水平学术专著,以推动相关领域的学术交流,促进学科发展,助力科技人才快速成长,建设战略科技领军人才后备军队伍。

为贯彻落实国家“科技强国”“人才强国”战略,进一步推动电子信息领域基础研究及技术的进步与创新,引导一线科研工作者树立学术理想、投身国家科技攻关、深入学术研究,人民邮电出版社联合中国电子学会、国务院学位委员会电子科学与技术学科评议组启动了“电子信息前沿青年学者出版工程”,科学评审、选拔优秀青年学者,策划“电子信息前沿专著系列”,计划分批出版约 50 册具有前沿性、开创性、突破性、引领性的原创学术专著,在电子信息领域持续总结、积累创新成果。“电子信息前沿青年学者出版工程”通过设立学术委员会和编辑出版委员会,以严谨的作者评审选拔机制和对作者学术写作的辅导、支持,实现对领域前沿的深刻把握和对未来发展的精准判断,从而保障系列图书的战略高度和前沿性。

“电子信息前沿专著系列”内容面向电子信息领域战略性、基础性、先导性的理论及应用。首期出版的10册学术专著,涵盖半导体器件、智能计算与数据分析、通信和信号及频谱技术等主题,包含清华大学、西安电子科技大学、哈尔滨工业大学(深圳)、东南大学、北京理工大学、电子科技大学、吉林大学、南京邮电大学等高等学校国家重点实验室的原创研究成果。

第二期出版的9册学术专著,内容覆盖半导体器件、雷达及电磁超表面、无线通信及天线、数据中心光网络、数据存储等重要领域,汇聚了来自清华大学、西安电子科技大学、国防科技大学、空军工程大学、哈尔滨工业大学(深圳)、北京理工大学、北京邮电大学、北京交通大学等高等学校国家重点实验室或军队重点实验室的原创研究成果。

本系列图书的出版不仅体现了传播学术思想、积淀研究成果、指导实践应用等方面的价值,而且对电子信息领域的广大科研工作者具有示范性作用,可为其开展科研工作提供切实可行的参考。

希望本系列图书具有可持续发展的生命力,成为电子信息领域具有举足轻重影响力和开创性的典范,对加快重要原创成果的传播、助力科研团队建设及人才的培养、推动学科和行业的创新发展都起到积极作用。同时,我们也希望本系列图书的出版能激发更多科技人才、产业精英投身到我国电子信息产业中,共同推动我国电子信息产业高速、高质量发展。

2024年8月22日

集成电路作为现代信息技术的基石,被誉为“工业粮食”,其发展对全球科技进步和经济增长具有深远影响。摩尔定律预测集成电路领域晶体管的集成密度每18~24个月增加一倍。然而,随着晶体管尺寸进入深亚微米乃至纳米阶段,传统MOSFET在尺寸微缩过程中遭遇了一系列物理瓶颈,如短沟道效应导致的静态功耗显著增加和工作频率趋于饱和等问题。这些问题使得摩尔定律的发展面临极限,促使学术界和工业界积极探索新的器件结构和工作机制,以突破传统晶体管的性能极限。

近年来,超陡亚阈值斜率晶体管成为低功耗电子器件领域的研究热点。相比传统MOSFET,超陡亚阈值斜率晶体管能够突破玻尔兹曼热力学极限,实现更低的亚阈值摆幅,从而在更低的工作电压下保持较大的开态电流,在下一代低功耗集成电路中具有巨大的应用潜力。超陡亚阈值斜率晶体管是指室温下亚阈值摆幅低于60 mV/dec的器件,其核心工作机理是通过改变载流子的输运机制或增强栅控能力,以突破传统MOSFET的玻尔兹曼热力学极限,显著降低静态功耗。目前,主要的超陡亚阈值斜率晶体管包括TFET、NC-FET、NEM-FET、I-MOS和Hyper-FET等。其中,TFET、NC-FET和Hyper-FET因与传统CMOS工艺有良好的兼容性,成为目前学术界研究的重点。然而,这3类器件面临诸多技术挑战。例如,TFET存在开态电流较小、双极导电现象严重等问题;NC-FET易出现电滞回线,且超陡亚阈值特性仅对应较窄的沟道电流范围;基于VO2相变材料的Hyper-FET则受限于阻值转换电压较大、开关比较低及对温度敏感等问题。

本书围绕超陡亚阈值斜率晶体管的关键性能优化展开研究,采用数值仿真、解析建模和实验制备相结合的方法,系统探讨超陡亚阈值斜率晶体管的工作原理、电学特性及工艺优化策略,以期为新型低功耗电子器件的设计提供理论支持。

本书共7章。第1章概述晶体管与集成电路的发展历史、超陡亚阈值斜率晶体管的研究现状和面临挑战等。第2章介绍环栅负电容隧穿场效应晶体管的解析模型和工作原理等。第3章重点分析硅基多栅负电容场效应晶体管的解析模型和应用等。第4章讨论2D沟道材料负电容场效应晶体管的实验制备、解析建模等。第5章研究负电容氧化物薄膜晶体管的实验制备及工艺优化。第6章提出一种新型负电容无结型场效应晶体管,深入分析该器件的数值仿真研究和解析模型。第7章详细探讨基于原子阈值开关的混合场效应晶体管的实验制备、电学特性、工作机理及应用。

为便于表述,全书对物理量与符号的使用作出说明:各章的物理量,在首次给出符号定义后,若在同一章内定义不变,则后续均以符号代替文字表述,跨章时则重新说明,以确保阅读的独立性与连贯性。同时,本书除2.1节外,在各类晶体管紧凑模型的推导过程中,所涉及的电场强度、极化强度等物理矢量均为一维形式。为简化公式推导过程,对此类矢量的一维分量,本书统一采用标量符号予以表征,特此说明。

本书的研究成果不仅为超陡亚阈值斜率晶体管的设计和优化提供了系统的理论依据,也为低功耗集成电路的发展提供了新的技术思路。希望本书能够为从事集成电路设计与研究的学者、工程师及相关领域的学生提供有益的参考。

在编写本书的过程中,我们得到了众多专家和学者的支持与帮助。在此,特别感谢人民邮电出版社顾慧毅、贺瑞君和林舒媛老师的宝贵指导。同时,衷心感谢清华大学梁仁荣老师和程为军博士对本书部分内容提出的建议。此外,家人的理解与支持也为完成本书提供了重要助力,在此一并致谢。

本书相关研究工作得到了广西自然科学青年基金项目(2023GXNSFBA026021)、广西科技基地和人才专项(桂科AD22035213)、国家自然科学基金项目(61904164、62464001和U24A20296)及广西师范大学高层次人才项目(2022TD005)的支持,在此深表感谢!

由于本书内容涉及物理、化学、材料等多个学科和领域,且作者水平有限,书中难免存在不足,恳请读者批评指正。

蒋春生

2025年8月于广西师范大学

集成电路(Integrated Circuit)是支撑现代经济社会发展的战略性、基础性和先导性产业,是引领新一轮科技革命和产业变革的关键力量。集成电路作为全球信息产业的基础和核心,是各国高科技发展水平的象征和大国科技博弈的战略制高点。集成电路也是我国目前被美国“卡脖子”的关键技术。因此,大力发展集成电路产业近年来已经成了我国的基本国策[1]。集成电路就是将电路元器件及它们的互连线一起制作在半导体衬底上所形成的独立电路系统,发展集成电路的目的在于把传统电路系统微型化,以提高芯片的性能和集成度。金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor,MOSFET)是大规模集成电路的基本组成单元。

一直以来,平面MOSFET的发展遵循摩尔定律,即集成电路上的晶体管数量每18~24个月增加一倍,性能提升一倍[2]。摩尔定律的物理基础是登纳德缩放定律(Dennard Scaling),即平面MOSFET的尺寸和工作电压等比例缩小,其他器件和电路参数(如衬底掺杂浓度、电容和功耗等)按相同比例增加或缩小。成本和性能是半导体产业界需要考虑的两个重要因素。MOSFET的尺寸微缩使得各种逻辑器件和存储器件的单管面积在不断缩小的同时,相应的性能(如工作频率)不断提升,因此MOSFET的尺寸微缩成为半导体产业发展的主要驱动力。从单晶体管发展到如今集成几十亿个晶体管的芯片,单晶体管的成本不断下降,这是因为随着晶体管的尺寸不断减小,单晶体管所需的版图面积不断缩小。然而,随着处理的信息规模越来越大和遇到的挑战越来越复杂,集成电路的规模需要不断扩大并且处理信息的速度必须越来越快。MOSFET的尺寸持续微缩就能很好地满足这种需求。依据登纳德缩放定律,MOSFET的尺寸按比例减小,单个芯片上可集成的晶体管数量大幅增加,单元电路的时延也随之减小,电路的工作速度提升。

随着晶体管特征尺寸缩小至100 nm以下,硅基MOSFET就不可避免地会遇到一些基本的物理问题,出现一些非理想的现象。这些非理想效应一般被称为短沟道效应,短沟道器件定义为沟道长度与源/漏区-沟道结耗尽区宽度相当的晶体管。经过产业界和学术界的共同努力,其中的大部分问题已经被很好地解决了[3]。例如,针对多晶硅栅的耗尽效应,提出了用金属栅替代的方案[4-5];针对栅介质隧穿漏电流显著增大的问题,提出了High-K介质方案[6-7];针对高电场导致沟道载流子迁移率下降的问题,研究者提出了能带工程,例如应变硅技术和GeSi合金技术[8],甚至直接选择一些与硅基互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺相兼容的高迁移率材料,例如锗和Ⅲ-Ⅴ族化合物半导体[9-10]。对于MOSFET存在的寄生电阻和寄生电容效应问题,则可以通过源漏工程、互连金属和隔离介质的优化等方法去解决。当平面MOSFET尺寸缩小到亚微米后,诸多短沟道效应凸显[11-13],包括阈值电压下降、源漏穿通(Punch-Through)、漏致势垒降低(Drain Induced Barrier Lowering,DIBL)效应和亚阈值摆幅(Subthreshold Swing)升高等。这些短沟道效应导致小尺寸MOSFET的关态电流显著增大。从深亚微米到如今的亚5 nm阶段,鳍式场效应晶体管(Fin Field-Effect Transistor,FinFET)技术很好地缓解了漏电这一问题[14-16],它通过将栅电场对沟道的控制维度从一维升级到三维(Three Dimension,3D),极大地增强了栅控能力。理想的栅控器件是围栅场效应晶体管(Gate-All-Around Field-Effect Transistor,GAAFET),其栅极完全包裹着沟道,在3 nm工艺节点以下,产业界很可能会采用这种理想的结构[3]。

遗憾的是,以上众多的性能改善技术仍然没能从根本上改变MOSFET中沟道载流子的输运机制,因为FinFET等多栅晶体管仍然是基于漂移-扩散(Drift-Diffusion)输运机制的场效应晶体管。场效应晶体管(Field-Effect Transistor,FET)的亚阈值摆幅,用符号SS表示,SS 2.3kT / q(k为玻尔兹曼常数,T为热力学温度,q为基本电荷),无法突破玻尔兹曼热力学极限(即室温下SS≥ 60 mV/dec),因此不能从根本上解决晶体管静态功耗过大的问题。在晶体管特征尺寸的微缩过程中,实际上晶体管的功耗密度是逐渐增加的[17]。在90 nm及以下工艺节点,以单位功耗密度衡量,尺寸微缩很难再带来性能的提升[18]。功耗密度的增加主要有两方面的原因:亚阈值漏电流的增大;电源电压无法等比例减小。由于电源电压无法随MOSFET的几何尺寸等比例减小,FET的SS无法随尺寸等比例降低,且会因为短沟道效应而显著升高,因此对于给定的晶体管电流驱动能力和电源电压,关态亚阈值漏电流会呈指数增大。当MOSFET的尺寸缩小到十几纳米甚至几纳米的时候,静态功耗所带来的影响已经超过了动态功耗。此外,在实际集成电路制造工艺迭代的过程中,相对晶体管尺寸的减小,电源电压的减小速度缓慢得多,这进一步导致芯片单位面积的动态功耗显著增加。

2.3kT / q(k为玻尔兹曼常数,T为热力学温度,q为基本电荷),无法突破玻尔兹曼热力学极限(即室温下SS≥ 60 mV/dec),因此不能从根本上解决晶体管静态功耗过大的问题。在晶体管特征尺寸的微缩过程中,实际上晶体管的功耗密度是逐渐增加的[17]。在90 nm及以下工艺节点,以单位功耗密度衡量,尺寸微缩很难再带来性能的提升[18]。功耗密度的增加主要有两方面的原因:亚阈值漏电流的增大;电源电压无法等比例减小。由于电源电压无法随MOSFET的几何尺寸等比例减小,FET的SS无法随尺寸等比例降低,且会因为短沟道效应而显著升高,因此对于给定的晶体管电流驱动能力和电源电压,关态亚阈值漏电流会呈指数增大。当MOSFET的尺寸缩小到十几纳米甚至几纳米的时候,静态功耗所带来的影响已经超过了动态功耗。此外,在实际集成电路制造工艺迭代的过程中,相对晶体管尺寸的减小,电源电压的减小速度缓慢得多,这进一步导致芯片单位面积的动态功耗显著增加。

当集成电路进入亚10 nm阶段,必须研究超陡亚阈值斜率晶体管,以求从根本上解决晶体管静态功耗过大的问题。超陡亚阈值斜率晶体管是指室温下SS < 60 mV/dec的器件,目前主要包括隧穿场效应晶体管(Tunnel FET,TFET)[19]、负电容场效应晶体管(Negative Capacitance FET,NC-FET)[20]、纳米机电场效应晶体管(Nano-Electro-Mechanical FET,NEM-FET)[21]、碰撞电离MOS器件(Impact-Ionization MOS,I-MOS)[22]和基于相变开关的混合场效应晶体管(Hybrid Phase Transition FET,Hyper-FET)[23]。其中,NEM-FET的可靠性问题比较严重;I-MOS需要较高的工作电压,因此不适用于低电压、低功耗的集成器件;TFET和Hyper-FET改变了源极和沟道之间载流子的输运机制;NC-FET则增强了栅电场对沟道表面的控制能力,实现了超陡亚阈值斜率特性,并且与传统硅基CMOS工艺兼容,引起了大量研究者的关注。这些器件可作为超陡亚阈值斜率逻辑开关器件。目前这几种器件面临着不少挑战,例如,TFET存在开态电流过小和双极导电现象严重等问题;NC-FET存在电容匹配和本征工作频率低等问题;基于VO2相变材料的Hyper-FET则受限于阻值转换电压较大、开关比较低及对温度敏感等问题。将来若想让超陡亚阈值斜率晶体管真正替代MOSFET,应用于超大规模集成电路,其超陡亚阈值摆幅对应的沟道电流应达到4~5个量级以上[24],目前TFET、NC-FET和Hyper-FET的性能还远未达到。本章将针对超陡亚阈值斜率晶体管存在的关键技术问题进行讨论,旨在提升超陡亚阈值斜率晶体管的核心性能,促使该类晶体管技术尽快成熟。

历史上,集成电路技术是在美国军方资助下发展起来的。美国为投资军用微电子技术,于1958年专门成立了美国国防部高级研究计划局(Defense Advanced Research Projects Agency,DARPA)。DARPA于1991年设立的下属机构微系统技术办公室负责通过对各类新型集成电路技术(如存算一体计算架构、微电子机械系统和光通信等)进行投资来创造具有颠覆性的军事技术。为了在不依赖登纳德缩放定律的情况下继续推进半导体器件和集成电路性能的大幅提升,保持美国领先的科技地位,DARPA于2017年6月启动了“电子复兴计划”(Electronics Resurgence Initiative,ERI),业界预测这项计划将开启下一次电子革命[25]。ERI是一个历时5年、总投资15亿美元的研究计划,美国商业界和国防工业界相关企业、大学研究人员和国防部之间会开展一系列具有前瞻性的合作项目,对下一代集成电路技术相关的材料、设计方案和架构等开展创新性研究。集成电路商业模式的鼻祖是1957年由戈登·摩尔(Gordon Moore)和罗伯特·诺伊斯(Robert Noyce)等“八大天才叛逆者”创立的仙童半导体公司,之后该公司所在地被称为硅谷。

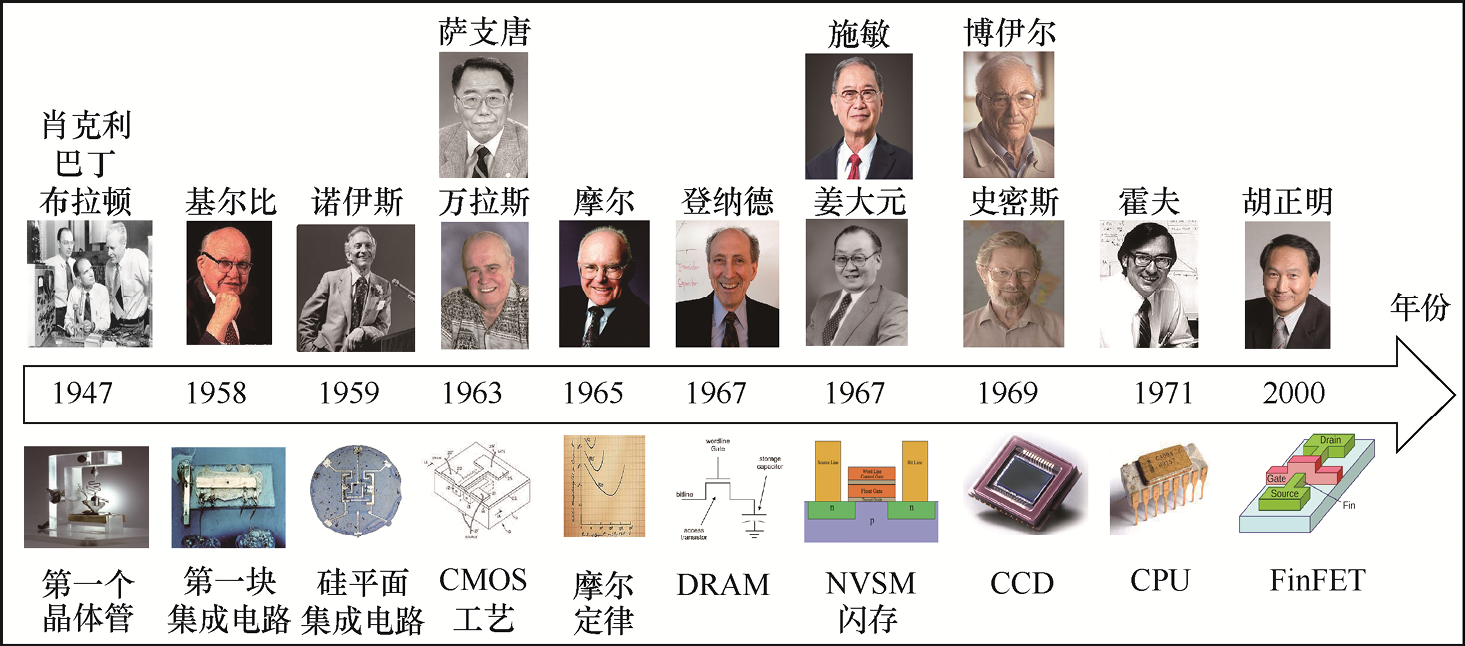

晶体管的发明要追溯到1926年,利林菲尔德(Lilenfeld)首先以专利形式提出了FET的概念[26],但限于当时的制造技术水平,半导体表面有很高的界面态,没能制成可商用的FET。最先问世的晶体管是在1947年,由贝尔实验室的威廉·肖克利(William Shockley)、约翰·巴丁(John Bardeen)和沃尔特·布拉顿(Walter Brattain)制造的点接触双极型晶体管[27],他们因此共同获得了1956年的诺贝尔物理学奖。在之后很长一段时间里,双极型晶体管几乎占据了整个商用晶体管领域。直到1960年,随着薄膜生长工艺水平的进步,第一个平面MOSFET才在贝尔实验室问世[28]。

集成电路的发明则要从1958年9月谈起,德州仪器的杰克·基尔比(Jack Kilby)研制出世界上第一块集成电路,成功实现把电子器件集成在一块半导体材料上的构想。2000年,基尔比因为发明集成电路而获得当年的诺贝尔物理学奖。更具有里程碑意义的是1963年CMOS工艺诞生。从此以后,除少数要求高频、大功率的领域外,MOSFET在大部分领域代替了双极型晶体管[29]。1971年,英特尔的特德·霍夫(Marcian Edward“Ted”Hoff)设计并制造出了第一款商用微处理器——4004,标志着人类正式进入“芯时代”。其他具有里程碑意义的发明如图1.1所示。为了进一步提高集成电路性能、降低制造成本,在过去几十年里,集成电路一直向着单个晶体管尺寸微缩和增大晶圆直径两个目标发展。

图1.1 集成电路技术发展历史上的重要发明

缩放定律最先是由登纳德(Dennard)提出来的,即平面MOSFET的物理尺寸和工作电压按相同比例缩小,沟道电场保持不变,其他物理量(如衬底掺杂浓度、电容、器件功耗和电路时延等)按相应比例增大或缩小,如表1.1所示[30]。其中,k为比例因子,且k < 1。

表1.1 基于恒定电场的缩放定律[30]

| 器件与电路参数 |

缩放比例 |

|---|---|

| 器件尺寸 |

k |

| 衬底掺杂浓度 |

1/k |

| 电压 |

k |

| 电场 |

1 |

| 载流子速度 |

1 |

| 耗尽层宽度 |

k |

| 电容 |

k |

| 漂移电流 |

k |

| 器件密度 |

1/k2 |

| 功率密度 |

1 |

| 器件功耗 |

k2 |

| 电路时延 |

k |

| 功率延时积 |

k3 |

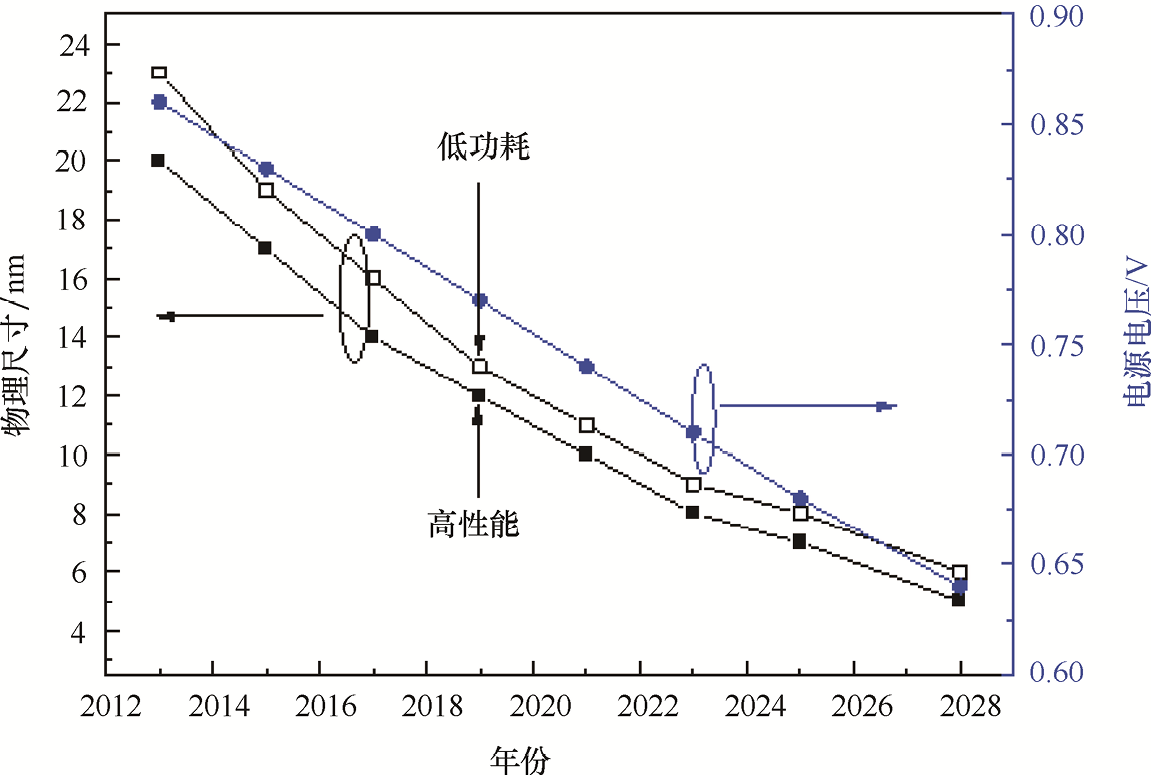

然而,如图1.2所示,国际半导体技术路线图(International Technology Roadmap for Semiconduct,ITRS)在2013年预测的集成电路工艺尺寸发展路线表明,在深亚微米阶段,工业界真实的半导体工艺节点并不能按理想的恒定电场规则持续缩减,且电源电压的减小速度慢于特征尺寸。一个原因是工业界的各级电子元器件厂商希望在较长的时间内有一个稳定的工作电压,以免因产品更新换代造成成本高昂和各种产品间接口标准的不同;另一个原因是,一些物理参数(如热电压和SS)无法按比例减小或降低。

图1.2 ITRS在2013年预测的集成电路工艺尺寸发展路线[31]

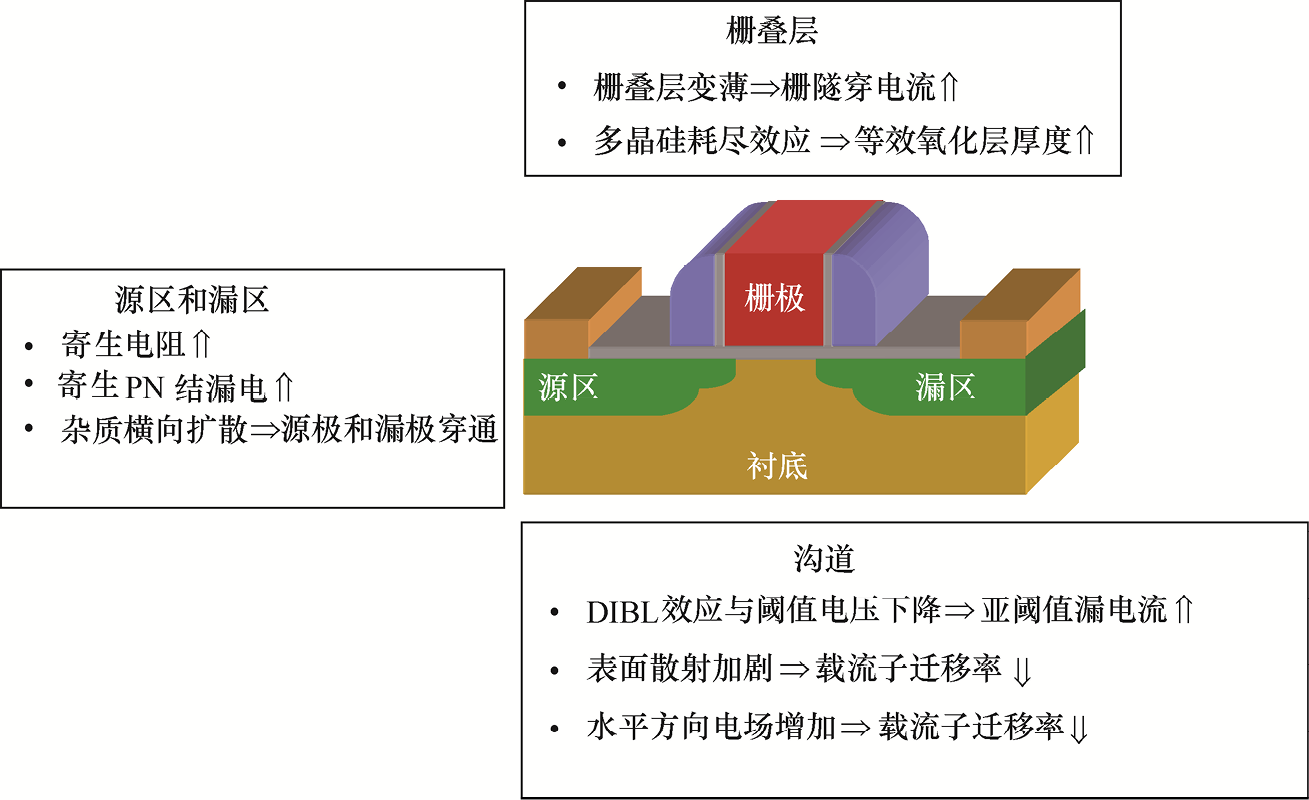

此外,如图1.3所示,平面MOSFET在缩小至深亚微米阶段时,遇到了很多严重的挑战:1)越来越薄的栅叠层使得栅隧穿电流很大[32-33],同时多晶硅耗尽效应不再可以被忽略[34-35],导致等效氧化层厚度增加;2)开态时,短沟道器件的源区和漏区寄生电阻增大,相对于沟道电阻不再可以被忽略;关态时,寄生PN结漏电非常显著;3)源区和漏区掺杂注入时,造成杂质往沟道横向扩散,极易导致短沟道器件的源漏极穿通[36-37];4)由于阈值电压下降和DIBL效应等短沟道效应产生的亚阈值漏电流非常大,导致小尺寸器件及其电路的静态功耗可以匹敌或超过动态功耗[13, 38-39],如此高的静态功耗导致了半导体元器件的发热,进一步导致器件性能的退化,加剧了电子系统的可靠性问题[40-41];5)沟道垂直电场加剧了沟道和栅介质界面的表面散射,进一步导致了沟道载流子迁移率下降。另外,水平方向电场增加导致的载流子速度饱和效应同样降低了载流子迁移率[42-43]。

图1.3 平面MOSFET在深亚微米阶段遇到的挑战

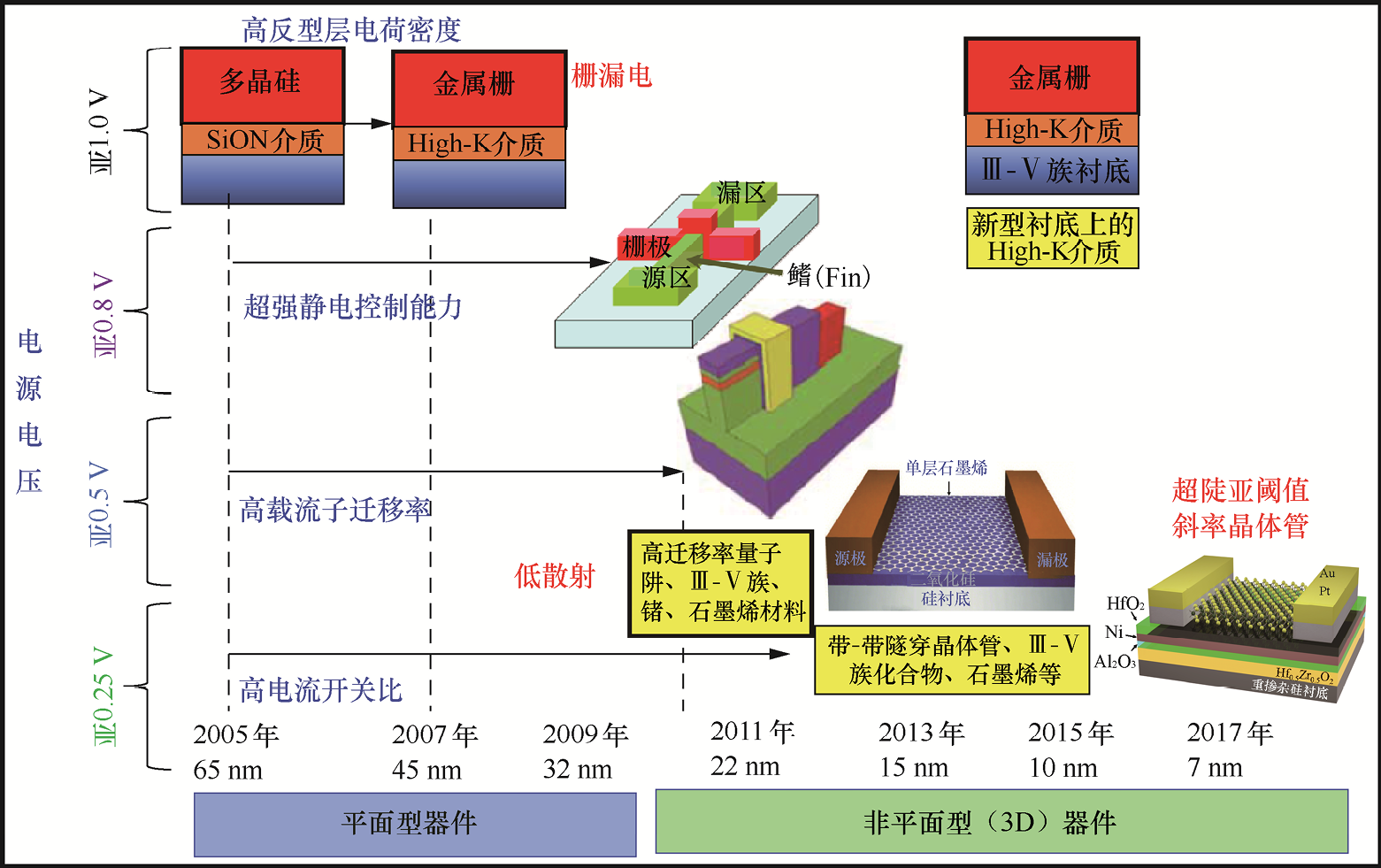

为了克服以上困难,延续摩尔定律,工业界与学术界试图从材料、器件结构等各个方面进行创新,如图1.4所示[44]。例如,采用高载流子迁移率的沟道材料和应变沟道技术来提高载流子迁移率,从而增大MOSFET的开态电流[8, 45-46];采用沟道轻掺杂或不掺杂技术来削弱杂质原子的涨落效应;采用High-K介质或金属栅技术来消除栅隧穿电流和多晶硅耗尽效应[6, 47]。事实上,目前由阈值电压下降和DIBL效应等短沟道效应引起的亚阈值漏电流及其导致的静态功耗是难以解决的实际问题。学术界和工业界最先提出采用多栅晶体管(如FinFET和GAAFET)来增强栅控能力,从而减小器件的亚阈值漏电流[16]。目前FinFET和GAAFET已成为工业界半导体3~22 nm工艺阶段主流的低功耗器件。然而,多栅晶体管仍然是基于漂移-扩散输运机制的MOSFET型器件,SS无法突破玻尔兹曼热力学极限。当集成电路进入亚10 nm阶段,必须研究超陡亚阈值斜率晶体管,以求从根本上解决晶体管的静态功耗问题。

图1.4 可能用来延续摩尔定律的新材料和新器件结构

尽管超陡亚阈值斜率晶体管在物联网、边缘计算和人工智能等低功耗领域展现出巨大的应用潜力,并在理论上具备显著优势,但其实际应用仍面临诸多挑战,包括器件性能的均一性、可靠性,与传统CMOS工艺的兼容性,以及高精度器件紧凑模型的缺失等。因此急需从新材料、新工艺、新结构等多个维度进行创新,以推动新型超陡亚阈值斜率晶体管早日实现产业化。

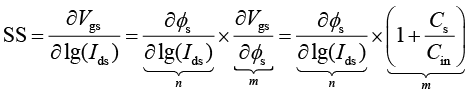

根据半导体器件的基础物理知识,可以知道:当MOSFET的开态电流一定时,亚阈值斜率越陡(即SS越低),则亚阈值区漏电流越小。超陡亚阈值斜率晶体管的工作原理可根据传统FET的 的定义来理解。

的定义来理解。

(1-1)

(1-1)

其中, 是栅源电压,

是栅源电压, 是漏源电流,

是漏源电流, 是表面势,

是表面势, 是沟道层单位面积电容,

是沟道层单位面积电容, 是绝缘缓冲层(在实际应用中,通常使用氧化层,如SiO2、HfO2等,作为绝缘缓冲层)单位面积电容。n是输运因子,反映的是沟道载流子的输运机制,例如,传统MOSFET是基于漂移-扩散输运机制的,

是绝缘缓冲层(在实际应用中,通常使用氧化层,如SiO2、HfO2等,作为绝缘缓冲层)单位面积电容。n是输运因子,反映的是沟道载流子的输运机制,例如,传统MOSFET是基于漂移-扩散输运机制的, ;而对于TFET和I-MOS,其载流子输运机制分别为带-带隧穿(Band-to-Band Tunneling)和碰撞电离,使得

;而对于TFET和I-MOS,其载流子输运机制分别为带-带隧穿(Band-to-Band Tunneling)和碰撞电离,使得 ;对于Hyper-FET,尽管基准FET内部的沟道载流子输运机制没有直接发生变化,仍为漂移-扩散输运机制,但载流子在通过与之串联的相变开关时,输运机制发生了变化,从而使室温下

;对于Hyper-FET,尽管基准FET内部的沟道载流子输运机制没有直接发生变化,仍为漂移-扩散输运机制,但载流子在通过与之串联的相变开关时,输运机制发生了变化,从而使室温下 ,因此整体上相当于n发生了变化。m是体因子,反映的是

,因此整体上相当于n发生了变化。m是体因子,反映的是 对

对 的调制能力。对于MOSFET,

的调制能力。对于MOSFET, 和

和 都是正值,所以m总大于1,部分情况下能无限接近1,例如采用绝缘体上硅薄膜(Silicon on Insulator,SOI)超薄体技术。对于NEM-FET和NC-FET,

都是正值,所以m总大于1,部分情况下能无限接近1,例如采用绝缘体上硅薄膜(Silicon on Insulator,SOI)超薄体技术。对于NEM-FET和NC-FET, 能小于0,故m可以小于1。表1.2为常见的几种超陡亚阈值斜率晶体管及其物理机制。I-MOS需要较高的工作电压,且难以缩小尺寸,不符合低功耗的要求[48];NEM-FET则有着严重的可靠性问题且转换速度有限[49]。因此,本节接下来主要介绍适用于低功耗和高可靠性应用的TFET、NC-FET和Hyper-FET的研究进展及其面临的挑战。

能小于0,故m可以小于1。表1.2为常见的几种超陡亚阈值斜率晶体管及其物理机制。I-MOS需要较高的工作电压,且难以缩小尺寸,不符合低功耗的要求[48];NEM-FET则有着严重的可靠性问题且转换速度有限[49]。因此,本节接下来主要介绍适用于低功耗和高可靠性应用的TFET、NC-FET和Hyper-FET的研究进展及其面临的挑战。

表1.2 常见的几种超陡亚阈值斜率晶体管及其物理机制

| 器件 |

物理机制 |

|

|---|---|---|

| TFET |

改变n |

带-带隧穿 |

| Hyper-FET |

相变引起的负微分电阻(Negative Differential Resistance,NDR)效应 |

|

| I-MOS |

碰撞电离 |

|

| NEM-FET |

改变m |

静电机械开关 |

| NC-FET |

负微分电容效应 |

|

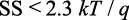

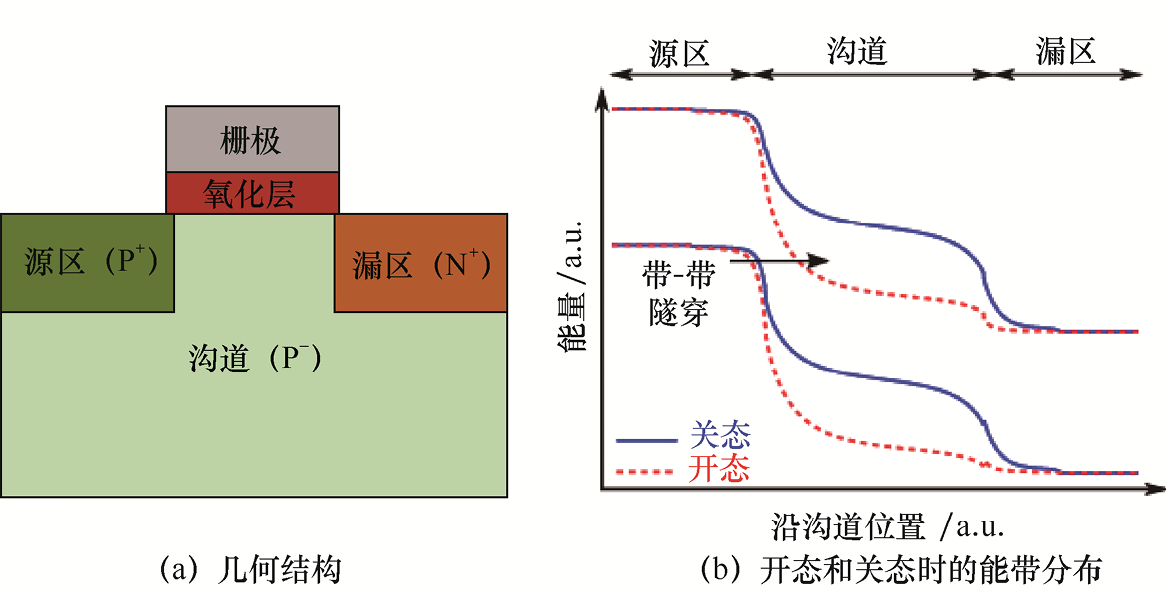

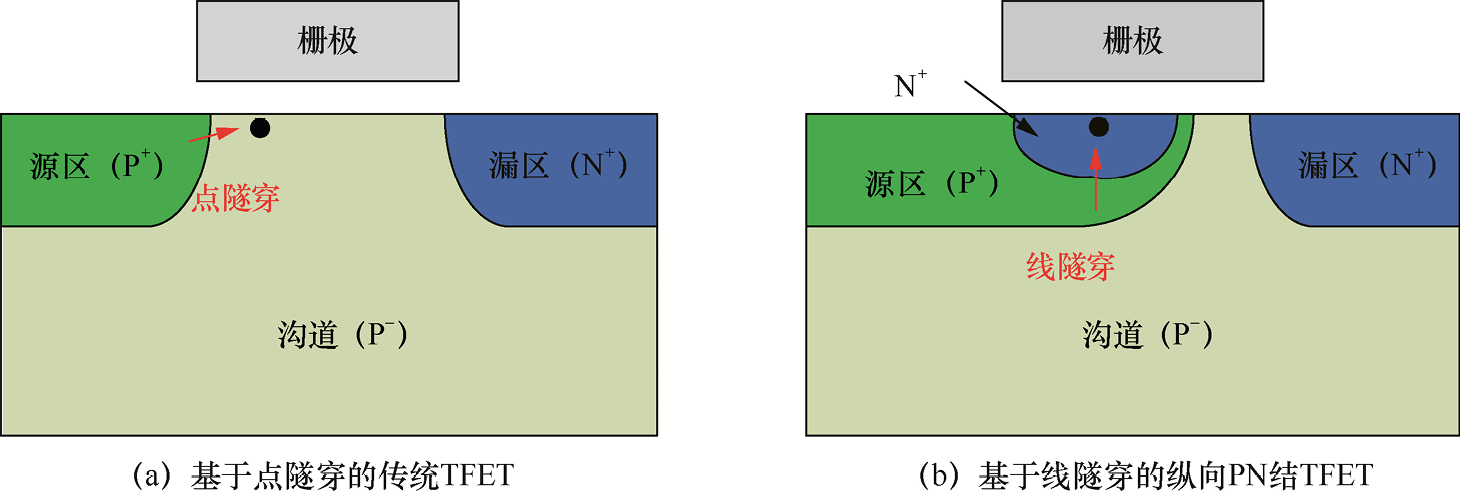

TFET是目前学术界研究得比较广泛的重要超陡亚阈值斜率晶体管。N型TFET的几何结构如图1.5(a)所示。传统的N型TFET是由栅电场控制的横向P+-I(或P-)-N+结构[19]。在关态时,TFET源区的价带与沟道的导带不重叠,不能发生有效带-带隧穿;在开态时,源区的价带顶与沟道的导带底对准,电子从源区隧穿到沟道,形成导通电流,如图1.5(b)所示。由于输运机制是价带电子到导带的载流子隧穿,这种机制不存在于传统MOSFET中。由载流子的玻尔兹曼分布导致的带尾效应可以完全被消除,并且有效隧穿发生在使能带重合的栅极和源区界面,所以TFET的开启特性可以很陡峭。隧穿发生的条件是源区的价带与沟道的导带发生能量重叠,这就需要本征或者轻掺杂沟道在栅电场的作用下发生反型,甚至是强反型现象,以形成N+导电层。N+导电层通常很薄,再加上隧穿概率与隧穿距离具有很强的负相关关系,这就导致隧穿发生在源区和沟道边界附近一层薄薄的强反型区内。较小的隧穿面积和隧穿概率导致器件的开态电流较小,一般传统TFET的开态电流比MOSFET的小2~4个量级[50-51],这也是传统TFET存在的一个局限。

图1.5 N型TFET

对于TFET,凯思公式(Kane’s Equations)是目前计算带-带隧穿概率时应用得最早和最广泛的模型[52-53]。

(1-2)

(1-2)

其中, 是载流子带-带隧穿概率,

是载流子带-带隧穿概率, 是普朗克常量,E是隧穿发生处的电场强度,

是普朗克常量,E是隧穿发生处的电场强度, 是载流子的隧穿有效质量,

是载流子的隧穿有效质量, 是硅沟道带隙宽度。D是一个与半导体材料带隙结构相关的参数,在直接带隙半导体材料中,数值一般为2;在间接带隙半导体材料中,数值一般为2.5[54]。从式(1-2)可知,想要增大TFET的带-带隧穿概率,可以从

是硅沟道带隙宽度。D是一个与半导体材料带隙结构相关的参数,在直接带隙半导体材料中,数值一般为2;在间接带隙半导体材料中,数值一般为2.5[54]。从式(1-2)可知,想要增大TFET的带-带隧穿概率,可以从 、

、 和E这些与器件材料和结构相关的参数出发,进行优化设计。实际上,与之相关的研究已有不少。例如,2011年,瑞士的Adrian M. Ionescu等人提出基于超薄SOI的TFET,实现了室温下SS = 42 mV/dec,关态电流密度为100 fA/μm [19];2017年,德国的S.GlaSS等人提出以SiGe作为源区空气桥的TFET,利用窄带隙半导体材料SiGe,实现了室温下SS < 60 mV/dec [55];2018年,瑞士的T. Rosca等人提出基于InAs/InGaASSb/GaSb的纳米线TFET阵列,GaSb与InGaASSb在源区形成异质隧穿结,增大能带弯曲程度,并且由于Ⅲ-Ⅴ族化合物半导体是直接带隙半导体,隧穿概率得到提升[56];2015年,美国的Deblina Sarkar提出基于二维(Two Dimension,2D)材料的TFET,利用2D材料的超薄特性,通过电场调控材料导电极性,可以实现较大的隧穿概率[57]。

和E这些与器件材料和结构相关的参数出发,进行优化设计。实际上,与之相关的研究已有不少。例如,2011年,瑞士的Adrian M. Ionescu等人提出基于超薄SOI的TFET,实现了室温下SS = 42 mV/dec,关态电流密度为100 fA/μm [19];2017年,德国的S.GlaSS等人提出以SiGe作为源区空气桥的TFET,利用窄带隙半导体材料SiGe,实现了室温下SS < 60 mV/dec [55];2018年,瑞士的T. Rosca等人提出基于InAs/InGaASSb/GaSb的纳米线TFET阵列,GaSb与InGaASSb在源区形成异质隧穿结,增大能带弯曲程度,并且由于Ⅲ-Ⅴ族化合物半导体是直接带隙半导体,隧穿概率得到提升[56];2015年,美国的Deblina Sarkar提出基于二维(Two Dimension,2D)材料的TFET,利用2D材料的超薄特性,通过电场调控材料导电极性,可以实现较大的隧穿概率[57]。

虽然采用窄带隙半导体材料、直接带隙半导体材料和2D材料提升了隧穿概率,但是也带来了一系列的问题和新的挑战。例如,尽管基于SiGe、Si等窄带隙半导体材料的TFET的开态电流较大,但是相应的亚阈值区漏电流和衬底漏电流增大了,导致关态电流较大。基于InAs、GaSb等直接带隙半导体材料的隧穿器件开态电流较大,但是材料的界面质量较差、缺陷较多,导致漏电流很大,电流开关比反而很小。而基于2D材料的隧穿器件首先面临的是材料的问题,即2D材料的规模制备和与传统CMOS制造工艺不兼容的问题有待解决;其次,在器件制备上,需要进一步研究2D材料与栅介质层的界面结构、稳定性和可靠性等问题。

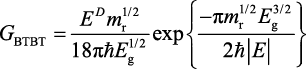

因此,除了采用先进的沟道材料,国际研究者从优化器件结构的角度出发,增大TFET的开态电流。2008年,美国加利福尼亚大学的胡正明教授在超大规模集成电路技术与电路研讨会(Symposium on VLSI Technology and Circuits)上提出了一种名为Green FET的pocket TFET[58],如图1.6(a)所示。在该结构中,源区向沟道延伸,与栅极部分重叠,在重叠区域中加入一个N+ pocket区。与传统TFET结构不同,在Green FET中,载流子隧穿的方向与栅电场方向一致,是在栅电场控制下的纵向PN结,而传统TFET的源极隧穿结可以理解为栅电场控制下的横向PN结。对于纵向PN结,整个结的界面都可以发生隧穿,大幅提升了隧穿面积,增大了隧穿电流。另外一种实现纵向PN结的办法是在栅极和源区的交叠处采用多步倾斜离子注入技术,然后利用杂质分凝技术在栅覆盖下形成一个超浅的P+N+结,如图1.6(b)所示[59],该方法也有效地增大了隧穿面积。2011年,北京大学黄芊芊等人提出了一种T形栅肖特基结TFET结构[60],通过引入肖特基结增大隧穿器件的开态电流,同时通过T型栅的设计,利用自耗尽效应减小了肖特基结的漏电流。2012年,黄芊芊等人又提出了一种增大栅控横向PN结隧穿电流的方法,该方法是将栅极做成条状结构,在单位栅宽的情况下,延长源区与沟道界面的长度,利用结耗尽作用增强隧穿结的能带弯曲程度,从而有效地增大了隧穿电流,如图1.6(c)所示[61]。垂直环栅TFET被认为是亚10 nm工艺节点实现低功耗CMOS集成电路的一个重要候选者,环栅结构能够增强栅控能力,有效抑制短沟道效应。利用环栅结构同样可以增强栅极对源极隧穿结的控制能力,如图1.6(d)所示[62]。

图1.6 不同结构的TFET

通过上面的分析,可以知道:在硅基TFET中,构造栅控的纵向PN结是增大TFET开态电流的有效方法,该方法对提升平面TFET的性能具有重要的意义。如图1.7(a)和图1.7(b)所示,通常将传统TFET的隧穿方式称为点隧穿,将纵向PN结TFET的隧穿方式称为线隧穿。从两个器件的横截面结构示意图中可以看出,传统TFET中带-带隧穿发生区域很小,因此被称为点隧穿;而在纵向PN结TFET中,带-带隧穿发生在结的整个界面上,隧穿面积较大,因此被称为线隧穿。线隧穿发生的方向与栅电场一致,隧穿面积大,开态电流与点隧穿的相比得到了大幅提升。线隧穿是增大TFET开态电流的一种十分有效的方式。目前关于带pocket区的Green FET的实验制备结果还很少,文献研究大多集中在TCAD数值仿真阶段。实验制备的难点在于如何获得超浅重掺杂的pocket区和减小所制备器件的关态电流。

图1.7 TFET的两种隧穿方式

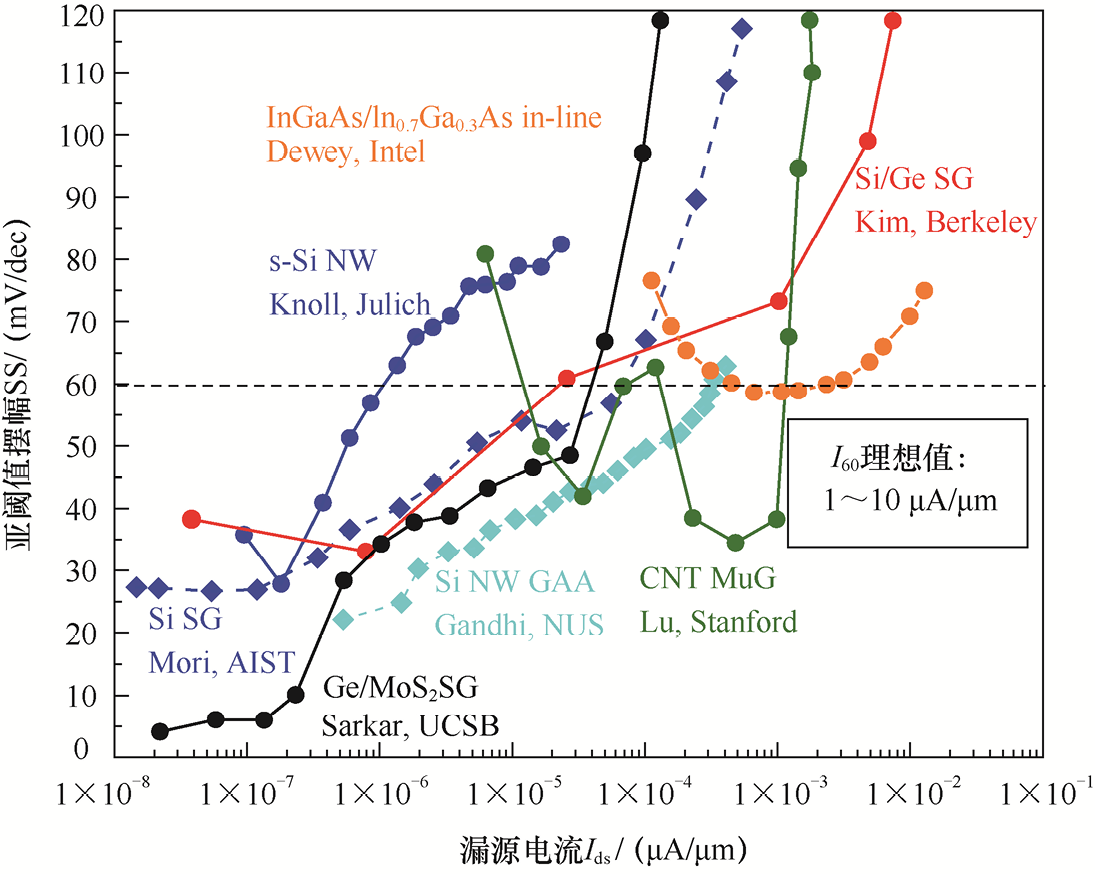

尽管研究者提出了许多增大TFET隧穿电流的方法,但是目前实验研究的开态电流还是不能达到与主流 MOSFET相媲美的程度。一个衡量TFET性能的重要指标是I60,定义为器件在SS = 60 mV/dec时的电流。美国圣母大学的Alan Seabaugh教授总结了2016年之前相关文献提到的部分TFET实验结果,如图1.8所示[24]。I60在理想情况下应该达到1~10 μA/μm,在4~5个量级的电流范围内,SS < 60 mV/dec。目前,I60的实验结果基本都小于1 nA/μm,远未达到上述要求。综合来看,目前硅基TFET存在的挑战主要在两个方面:开态电流较小;超陡亚阈值摆幅对应的沟道电流范围较小,即I60较小。

图1.8 2016年之前相关文献提到的部分TFET实验结果

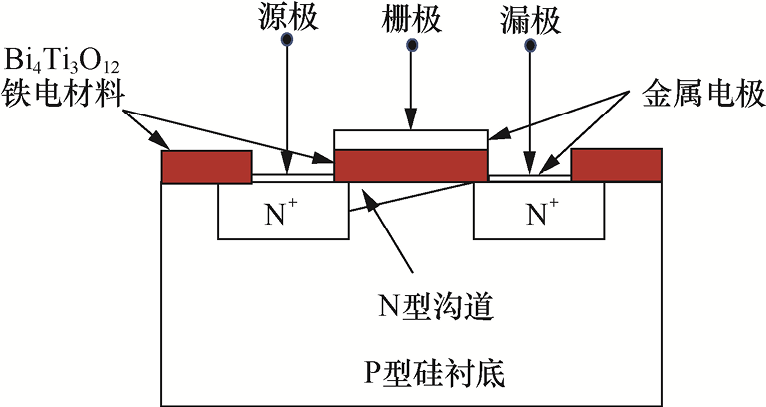

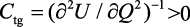

虽然NC-FET的概念直到2008年才由Salahuddin等人提出[20],但用于NC-FET栅介质的铁电材料早已被广泛研究,目前其主要的应用领域是铁电存储器,即FeFET非易失性存储器[48]。铁电NC-FET的几何结构与FeFET非易失性存储器完全一样,见图1.9。FeFET非易失性存储器利用了铁电材料在撤掉外加电场时,具有剩余极化(Residual Polarization)的特性,但由于其存储电荷保持时间较短,至今还未实现较大规模的商业化应用。铁电NC-FET与FeFET非易失性存储器的不同之处在于:铁电NC-FET主要应用于铁电材料电畴极化反转过程中的不稳定区域,这段不稳定区域呈现负微分电容,通过给铁电材料的负电容串联一个常规的正电容,使之稳定,铁电NC-FET工作电压较低,通过小心地设计器件结构,可以避免出现电滞回线,铁电NC-FET需要的铁电材料较薄,主要用于低功耗开关逻辑电路;而FeFET非易失性存储器的主要应用体现在铁电材料极化特性曲线(P-E曲线)的两个稳态上,需要电滞回线以获得较宽的存储窗口,且工作电压较高,铁电材料较厚。本章后续将展示通过合理的电容匹配技术,使铁电晶体管分别工作在NC-FET要求的开关逻辑状态和FeFET非易失性存储器要求的存储状态下。

图1.9 1974年Shu-Yau Wu提出的FeFET[48]

目前文献研究最多的NC-FET就是铁电NC-FET。根据栅叠层分类,铁电NC-FET可以分为金属-铁电-金属-绝缘体-半导体(Metal-Ferroelectric-Metal-Insulator-Semiconductor,MFMIS)结构和金属-铁电-绝缘体-半导体(Metal-Ferroelectric-Insulator-Semiconductor,MFIS)结构。根据栅数目分类,可以分为单栅(Single-Gate,SG)、双栅(Double-Gate,DG)和环栅(Gate-All-Around,GAA)结构等。根据衬底分类,则包括体(Bulk)衬底和SOI衬底结构。根据沟道材料分类,可以分为硅基、锗基和2D沟道材料NC-FET等。研究者还提出了其他类型的NC-FET,比如压电NC-FET[49]、NEM-FET和反铁电NC-FET[63-64]等。对于铁电NC-FET,尽管已有不少的研究文献,涉及负电容效应实验验证、NC-FET制备、数值仿真与解析模型建立等,但总体来说,相关工作不成熟且不成体系。例如,实验上至今也没有实现室温下SS < 60 mV/dec且无电滞回线的铁电NC-FET,器件的工作频率也没有超过10 MHz。理论上预测的铁电NC-FET的性能也存在不足,例如,理论预测室温下SS < 60 mV/dec的电压或电流范围非常窄且设计条件苛刻,但实验在很宽的电流范围内观察到了室温下SS < 60 mV/dec且伴有不同程度的电滞回线。压电NC-FET、NEM-FET和反铁电NC-FET等还都处在概念刚提出阶段,不管是实验还是理论模型都极其匮乏。

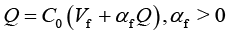

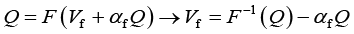

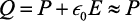

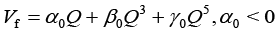

图1.10(a)展示了2018年由美国普渡大学Salahuddin等人首先提出的“概念型”器件,即金属-铁电-半导体(Metal-Ferroelectric-Semiconductor,MFS)结构NC-FET[20]。容易看出,除了将栅叠层中的传统氧化物绝缘栅介质换成了具有自极化效应的铁电材料,其结构与传统的MOSFET并无区别。MFS结构在实际制备工艺中不可能实现,因为这种方法会形成高浓度界面陷阱态,恶化器件性能。因此,在后续的实验和理论研究中,很少有人提到MFS结构NC-FET。为了简单地说明器件的工作原理,假设器件平带电压为0 V,在栅极上外加一个正电场,并且从0 V慢慢增大到一个较大电压Vdd时,在外加电场的作用下,由于铁电材料的自极化效应,原本混乱排列的电偶极子排列整齐,在铁电材料中形成了很强的极化强度P,并在铁电材料两端的电极板上感应出了大量的极化电荷,见图1.10(b)。这个过程明显是一个正反馈的过程,对于一阶近似,面电荷密度Q可以用如下公式描述。

(1-3)

(1-3)

其中, 为铁电层压降,

为铁电层压降, 为正反馈系数,

为正反馈系数, 为电容。实际的极化反转过程是一个高度的非线性过程。考虑高阶近似,则有

为电容。实际的极化反转过程是一个高度的非线性过程。考虑高阶近似,则有

(1-4)

(1-4)

其中,F是一个非线性函数。实际上,根据描述铁电材料相变的朗道-克朗尼克夫理论(Landau-Khalatnikov Theory,简称L-K理论)[65],若 非常大,则

非常大,则 ,则有

,则有

(1-5)

(1-5)

也就是说L-K理论能用来描述这个正反馈过程。其中, 、

、 和

和 是取决于具体铁电材料性质与厚度的参数。式(1-5)表现为图1.10(c)中的红虚线,曲线左上部分从A到B的过程对应上面提到的外加电场从0 V增大到Vdd的过程。由图1.10(c)知,在这个过程中,铁电层单位面积电容(

是取决于具体铁电材料性质与厚度的参数。式(1-5)表现为图1.10(c)中的红虚线,曲线左上部分从A到B的过程对应上面提到的外加电场从0 V增大到Vdd的过程。由图1.10(c)知,在这个过程中,铁电层单位面积电容( )是负的。尽管通常情况下这个负电容区是不稳定的,因为这个区域的吉布斯自由能密度

)是负的。尽管通常情况下这个负电容区是不稳定的,因为这个区域的吉布斯自由能密度 为凸函数,即处于高位,见图1.10(d)。但Salahuddin等人认为当负的铁电电容串联一个常规的正电容,使整个系统储存的能量在负电容区为凹函数,即对应总的栅电容

为凸函数,即处于高位,见图1.10(d)。但Salahuddin等人认为当负的铁电电容串联一个常规的正电容,使整个系统储存的能量在负电容区为凹函数,即对应总的栅电容 时,这个负电容区就能稳定[20]。图1.10(c)中带箭头的黑色虚线表示在孤立状态下,实验中铁电材料通常观察到的电滞回线。

时,这个负电容区就能稳定[20]。图1.10(c)中带箭头的黑色虚线表示在孤立状态下,实验中铁电材料通常观察到的电滞回线。

图1.10 MFS结构NC-FET的工作原理

在实验中直接验证负电容效应,主要有两种方法。

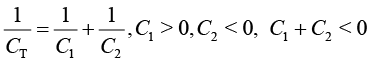

第一种是将常规正电容介质材料C1与负电容铁电材料C2串联,通过设置适当的材料厚度与温度,使整个系统的U为凹函数,使负电容区稳定,从而观察到总的串联电容 比C1大的现象[66-67],如式(1-6)式和(1-7)所示。

比C1大的现象[66-67],如式(1-6)式和(1-7)所示。

(1-6)

(1-6)

(1-7)

(1-7)

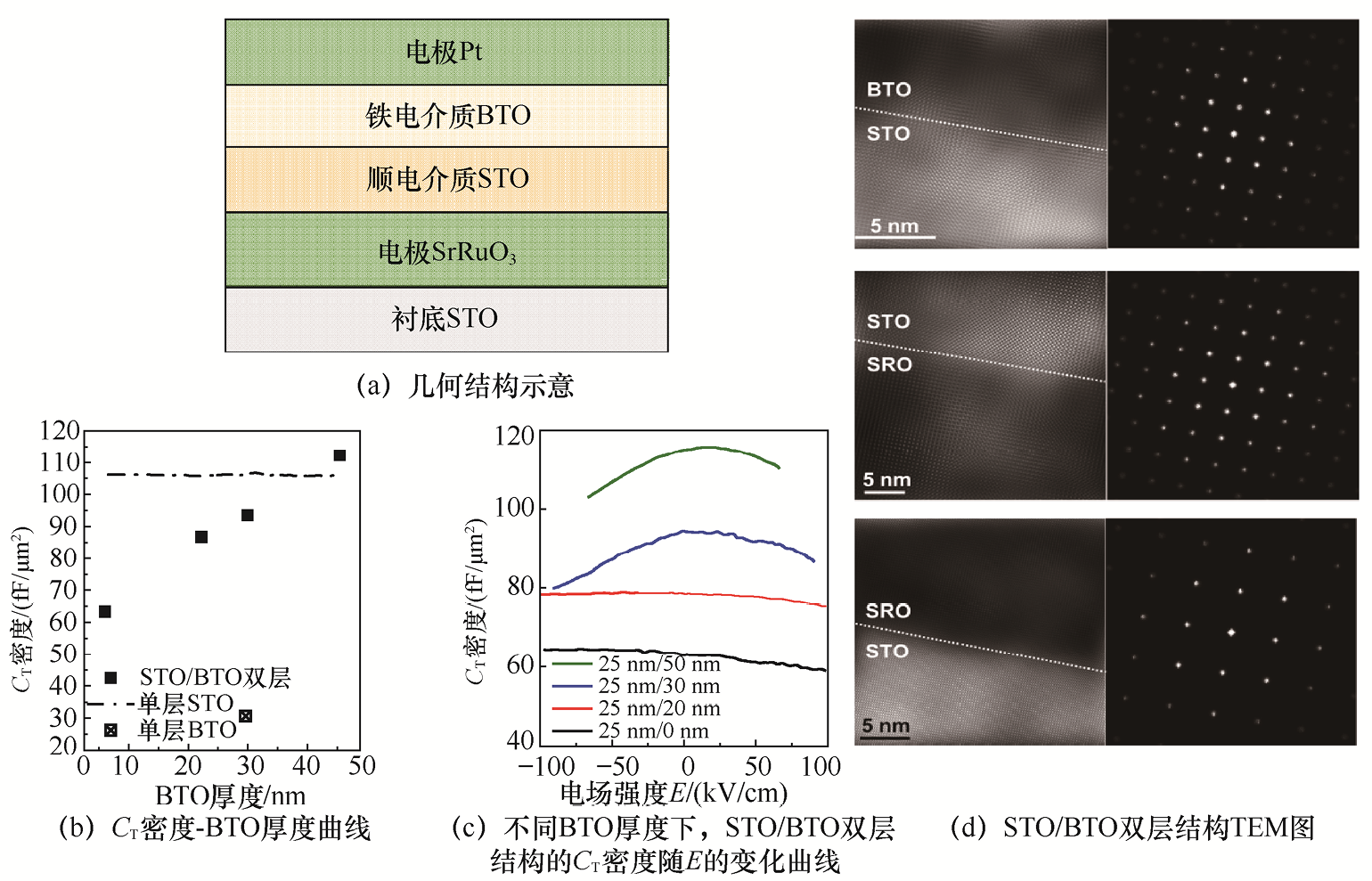

2014年,英国纽卡斯尔大学的Daniel J. R.小组在钛酸锶(SrTiO3,简称STO)衬底上制备了一个STO正电容与一个钛酸钡(BaTiO3,简称BTO)铁电负电容串联的器件,首先验证了第一个方法的可行性[67],双电容串联的器件结构如图1.11所示。STO在室温下为顺电相,呈现正电容,记为C1。而BTO的居里温度较高,约为395 K,室温下呈现铁电相,电容为负值,记为C2。两个介质层的总电容记为 。用钌酸锶(SrRuO3,简称SRO)做底电极是因为其晶格常数与STO衬底较匹配。不同材料界面的透射电子显微镜(Transmission Electron Microscope,TEM)图显示各界面质量良好,晶格匹配度高。在实验中,STO的厚度为25 nm,BTO的厚度分别为0 nm、20 nm、30 nm与50 nm。图1.11(b)所示为

。用钌酸锶(SrRuO3,简称SRO)做底电极是因为其晶格常数与STO衬底较匹配。不同材料界面的透射电子显微镜(Transmission Electron Microscope,TEM)图显示各界面质量良好,晶格匹配度高。在实验中,STO的厚度为25 nm,BTO的厚度分别为0 nm、20 nm、30 nm与50 nm。图1.11(b)所示为 密度随BTO厚度的变化,结果与L-K理论预计的一致,

密度随BTO厚度的变化,结果与L-K理论预计的一致, 密度随BTO厚度增加而增大,同时反映了

密度随BTO厚度增加而增大,同时反映了 >C1。图1.11中并未观察到电滞回线,证明了负电容效应的存在。

>C1。图1.11中并未观察到电滞回线,证明了负电容效应的存在。

图1.11 双电容串联的器件结构

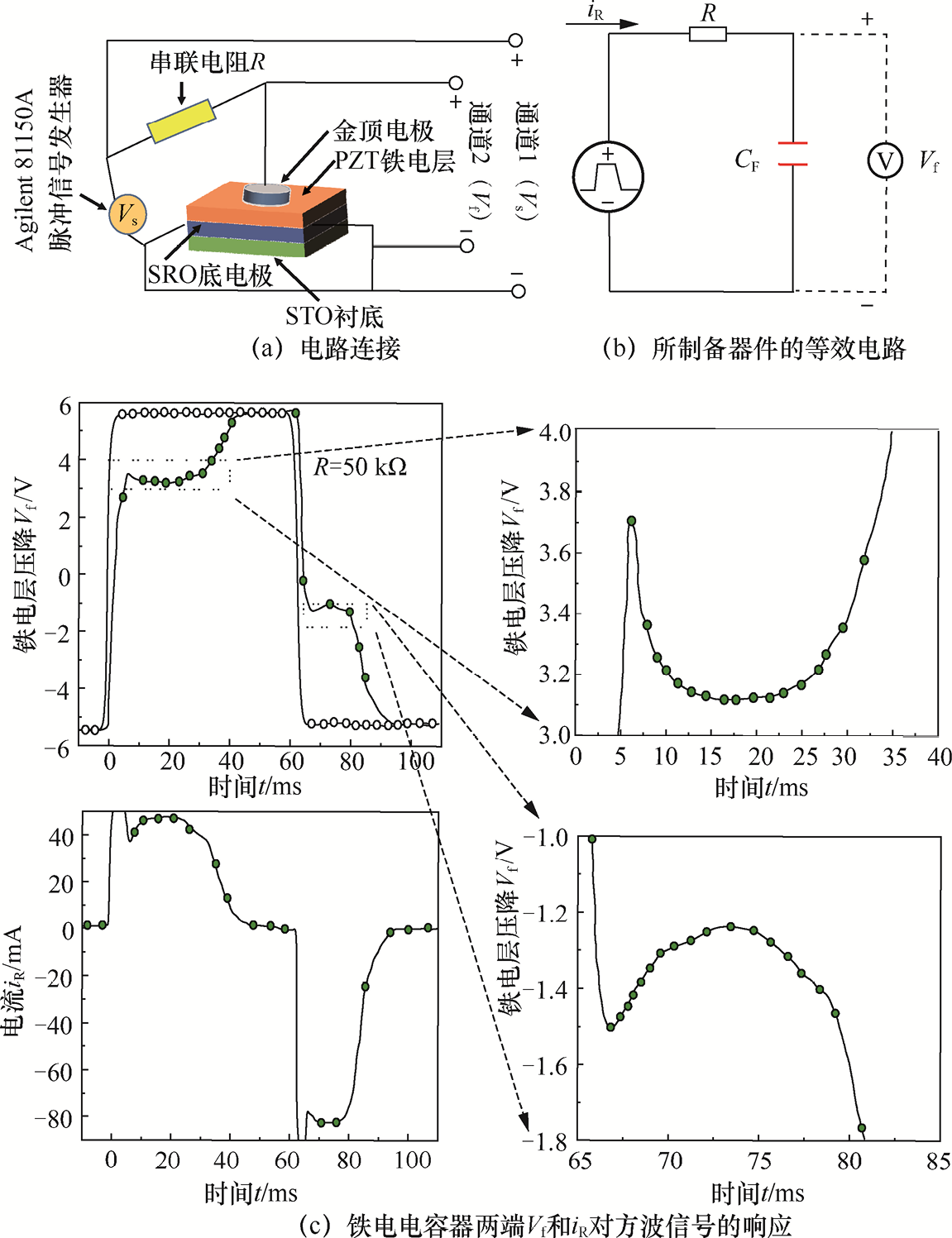

第二种是将铁电电容器与电阻串联起来,利用RC回路特有的瞬态特性来观察负电容现象。如果电容为负值,则RC回路的时间常数为负,会表现出不同于传统RC回路的充放电特性[68-70]。2015年,美国加利福尼亚大学伯克利分校的Salahuddin课题组创造性地提出用RC回路来验证负电容效应[68]。在他们的实验中,锆钛酸铅(Lead Zirconate Titanate,PZT)被用作铁电材料。铁电电容器串联了一个50 kΩ的电阻,如图1.12(a)和图1.12(b)所示。电源电压为 ,铁电电容器电容记为

,铁电电容器电容记为 。当一个方波信号加在RC回路两端时,铁电电容器的压降

。当一个方波信号加在RC回路两端时,铁电电容器的压降 和流经电阻的电流

和流经电阻的电流 对方波信号的响应被示波器记录,如图1.12(c)所示。从图1.12(c)中可以观察到,常规RC回路充放电过程是单调的,而铁电电容器两端的

对方波信号的响应被示波器记录,如图1.12(c)所示。从图1.12(c)中可以观察到,常规RC回路充放电过程是单调的,而铁电电容器两端的 和

和 对方波信号的响应不是单调的,存在凹陷或突包。这是因为这个电路的时间常数在部分区域是负值。这种独特的RC回路充放电特性证明了负电容效应的存在。

对方波信号的响应不是单调的,存在凹陷或突包。这是因为这个电路的时间常数在部分区域是负值。这种独特的RC回路充放电特性证明了负电容效应的存在。

图1.12 包含铁电层的RC结构瞬态响应测试

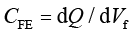

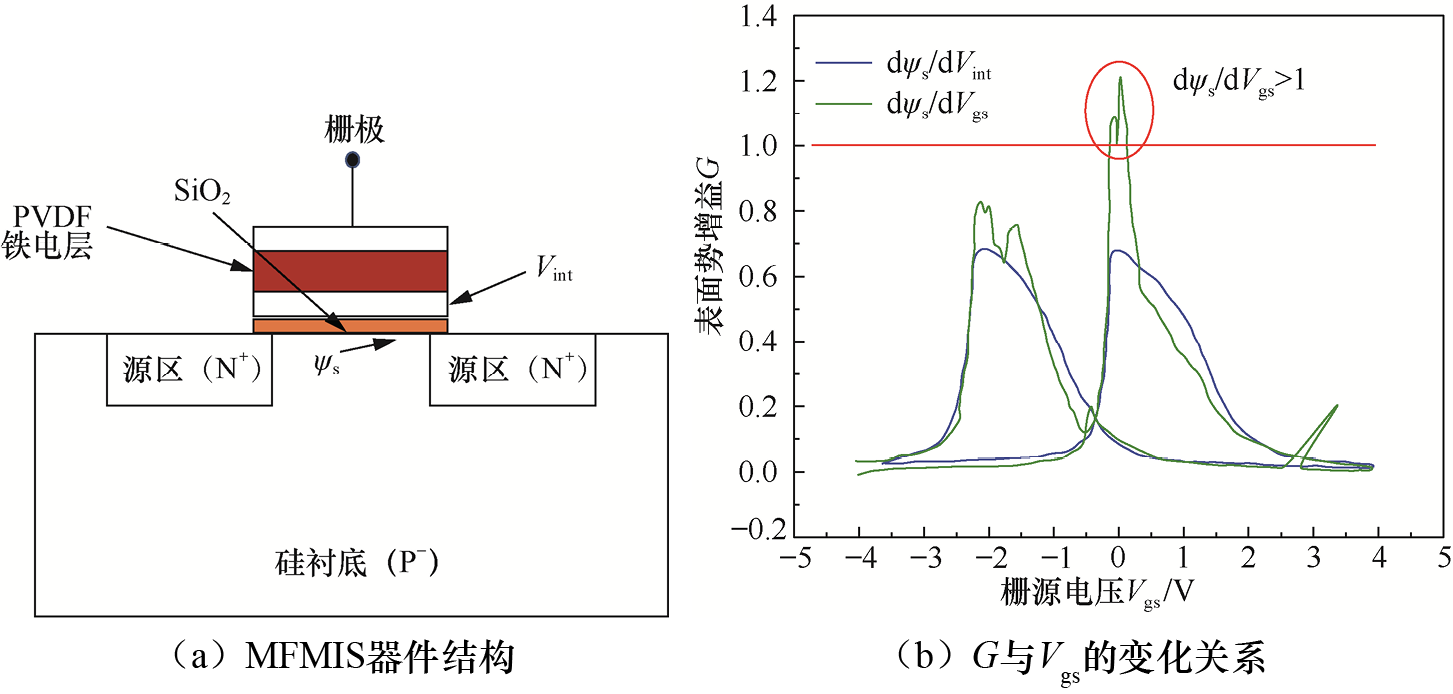

铁电NC-FET是最早被提出来的NC-FET,相对于其他类型的NC-FET,学术界对它的研究最多,其应用也相对比较成熟。根据栅叠层结构不同,铁电NC-FET可以分为MFMIS结构[71-73]与MFIS结构[74-76]。每个结构有各自的优点与缺点。两种结构中绝缘缓冲层的作用是阻止铁电材料与沟道半导体材料原子间的互相扩散,防止发生可能的化学反应,避免沟道表面态恶化[77]。MFMIS结构的一个优点是容易将半导体内部节点电势接到电学仪器上,通过观察半导体内部节点电势 相对于

相对于 的表面势增益G(G =

的表面势增益G(G = )是否大于1来探测是否存在负电容效应。另一个优点是能使绝缘缓冲层与铁电层界面的电荷较均匀地分布,避免绝缘缓冲层被击穿,同时增大内部金属栅和单位栅宽寄生电容,以提高电容匹配程度[78]。2010年,瑞士洛桑联邦理工学院的Rusu A.等人首先采用了这种结构[72],如图1.13(a)所示,SiO2用作缓冲层,有机薄膜聚偏二氟乙烯(Polyvinylidene Fluoride,PVDF)用作铁电材料,

)是否大于1来探测是否存在负电容效应。另一个优点是能使绝缘缓冲层与铁电层界面的电荷较均匀地分布,避免绝缘缓冲层被击穿,同时增大内部金属栅和单位栅宽寄生电容,以提高电容匹配程度[78]。2010年,瑞士洛桑联邦理工学院的Rusu A.等人首先采用了这种结构[72],如图1.13(a)所示,SiO2用作缓冲层,有机薄膜聚偏二氟乙烯(Polyvinylidene Fluoride,PVDF)用作铁电材料, 代表内部金属栅电势。如图1.13(b)所示,可以观察到器件的G大于1,表明所制备器件出现了负电容效应。

代表内部金属栅电势。如图1.13(b)所示,可以观察到器件的G大于1,表明所制备器件出现了负电容效应。

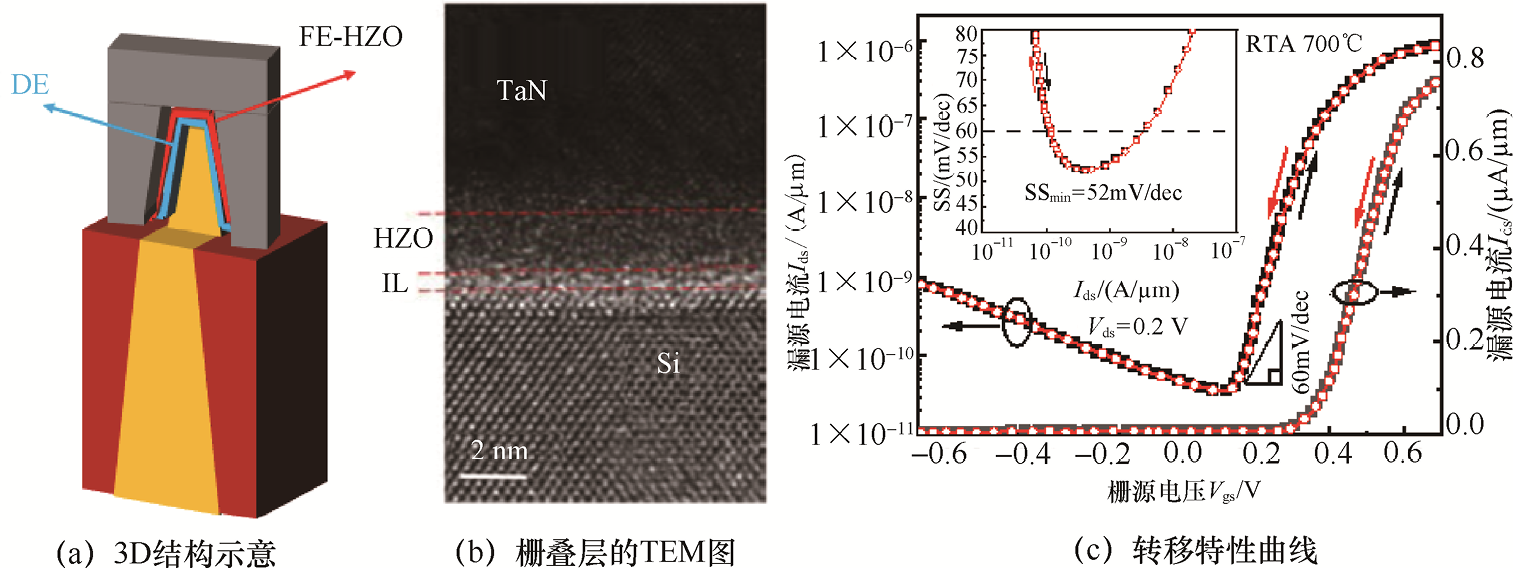

图1.13 MFMIS结构

MFMIS结构同样存在缺点:1)对于低功耗应用,这种结构是不合适的,因为悬浮在绝缘缓冲层与铁电层间的内部金属栅电位是不确定的,极容易受外界影响[78],导致电路逻辑运算出错;2)MFMIS结构还会通过增加瞬态漏电流降低铁电材料负电容区的稳定性[79],当工作电压较大时,沟道电子容易通过隧穿效应被注入内部金属栅,导致器件的转移特性曲线存在一定电滞回线,类似浮栅存储器[80]。在逻辑开关应用中,应该避免出现任何电滞回线,故更具有实际应用价值的是MFIS结构[74-76]。2016年,Lee M. H.等人制备的14 nm NC-FET就是MFIS结构,如图1.14所示。实验在700℃下进行快速热退火(Rapid Thermal Annealing,RTA)。该器件在室温下最小亚阈值摆幅SSmin = 52 mV/dec,接近无电滞回线,阈值电压 的偏移量为0.8 mV,展现出较好的电学特性[76]。MFIS结构的缺点是沟道层单位面积电容随

的偏移量为0.8 mV,展现出较好的电学特性[76]。MFIS结构的缺点是沟道层单位面积电容随 变化太敏感,容易导致非恒定的铁电电容、绝缘缓冲层电容与沟道层单位面积电容的失配,使室温下SS < 60 mV/dec的

变化太敏感,容易导致非恒定的铁电电容、绝缘缓冲层电容与沟道层单位面积电容的失配,使室温下SS < 60 mV/dec的 (或

(或 )的范围太小[78]。

)的范围太小[78]。

图1.14 MFIS结构NC-FET原型器件

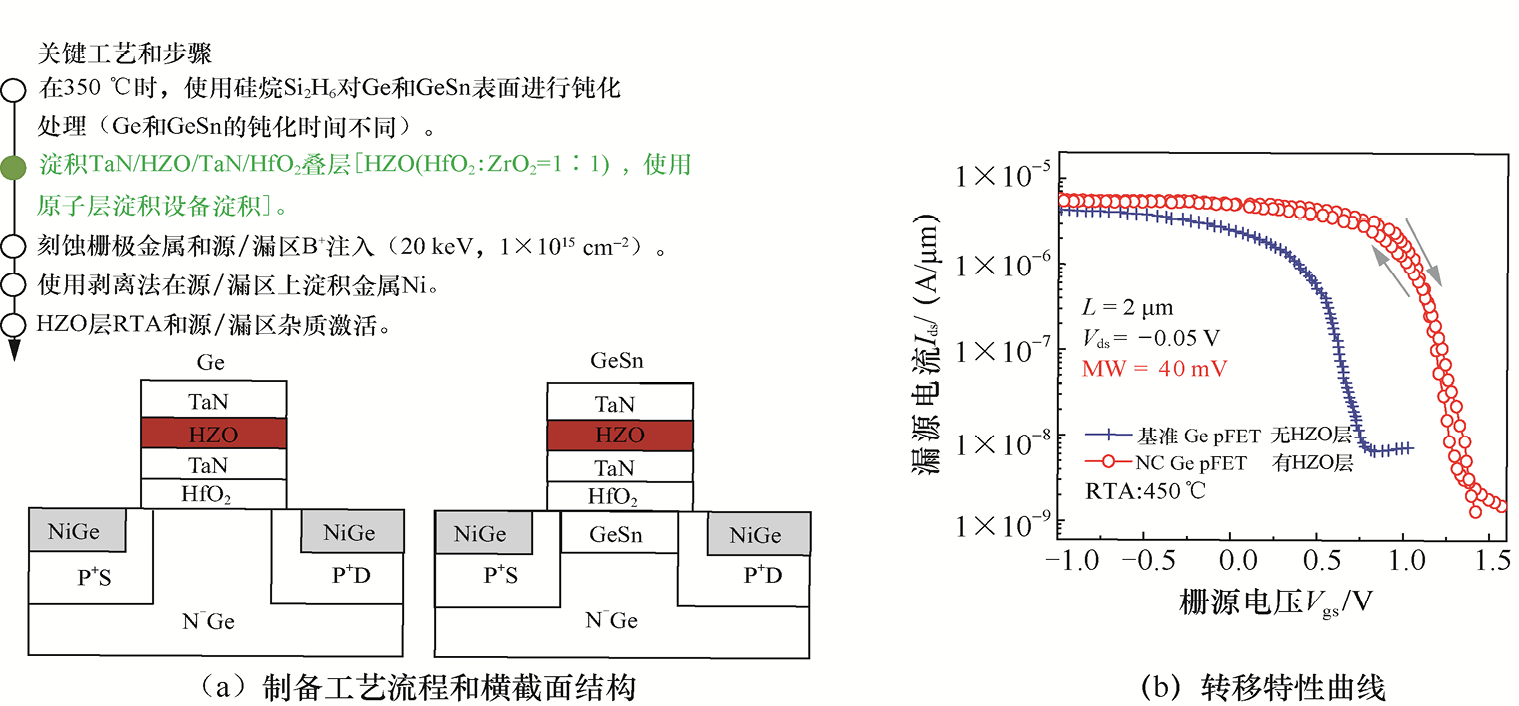

除了硅基NC-FET,研究者也研究了以高迁移率材料锗(Ge)和锗锡(GeSn)为沟道材料的NC-FET[81-82]。西安电子科技大学的周久人等人最先制备出Ge和GeSn沟道的NC-FET[81],器件栅长L为2 μm,如图1.15所示。室温下SSmin = 56 mV/dec且电滞回线窗口(Memory Window)仅为40 mV,性能达到国际前沿水平。实验中,他们观察到了NDR效应,这是由单位栅宽寄生电容引起的[83]。但N型Ge和GeSn沟道的NC-FET还没有人制备出来,离制备实用的CMOS工艺FET还有一定距离。综合来看,目前NC-FET技术仍存在两个重要挑战:一个是易出现电滞回线,另一个是满足电容匹配条件的沟道电流范围太小。

图1.15 Ge与GeSn沟道的NC-FET

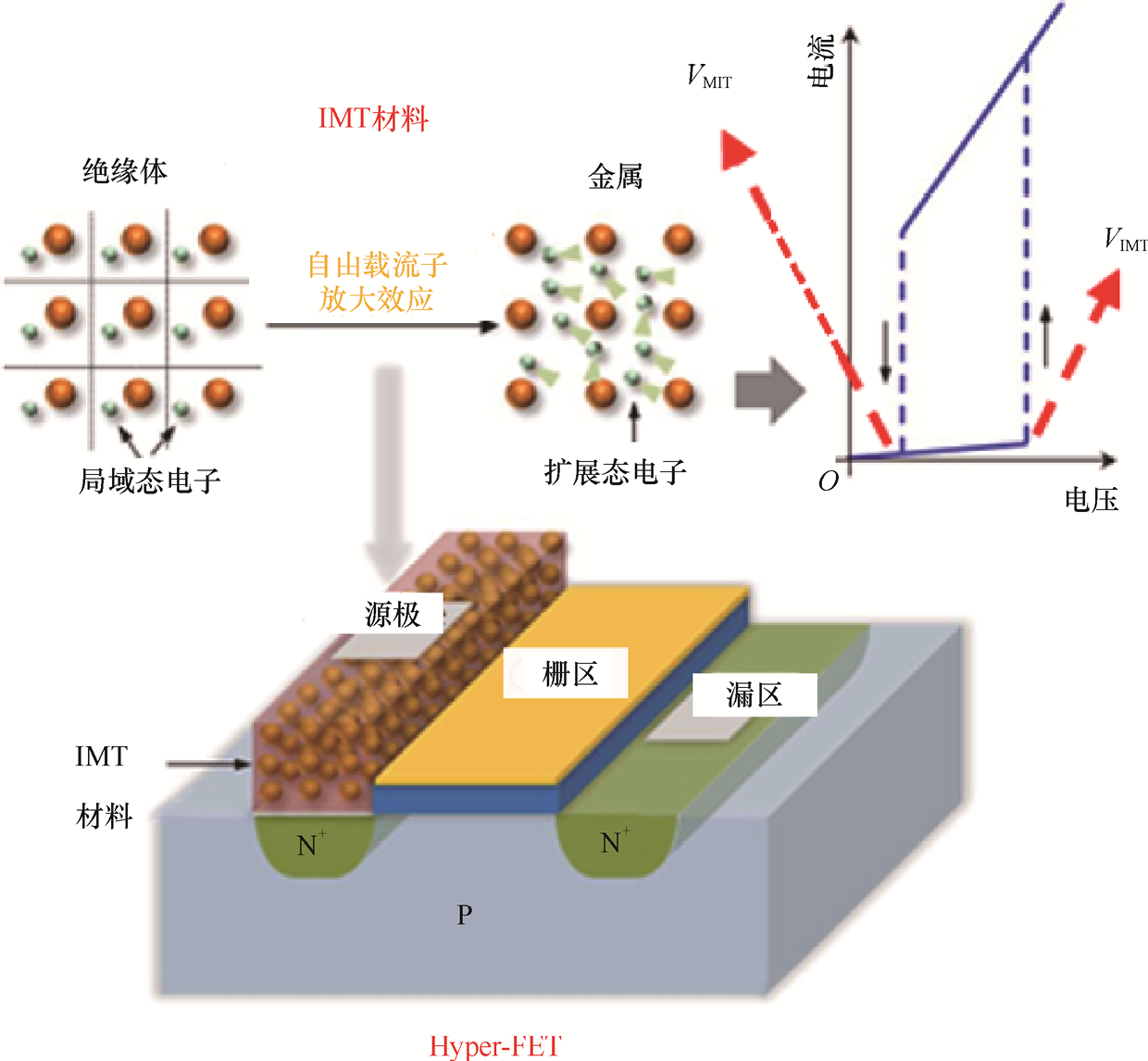

2015年,美国宾夕法尼亚大学的Suman Datta等人提出了Hyper-FET[23]。Hyper-FET是一种由 触发的开关器件,在

触发的开关器件,在 的调节下能够实现关态到开态的陡峭转换,以及能在很大的电流范围内实现超陡亚阈值斜率特性。图1.16是绝缘体-金属相变(Insulator-to-Metal Phase Transition,IMT)材料的工作机理与Hyper-FET的结构示意,Hyper-FET通过在传统MOSFET的源极串联一个由IMT材料构成的非线性电阻实现。当IMT材料两端的电压增大且超过正向转换电压

的调节下能够实现关态到开态的陡峭转换,以及能在很大的电流范围内实现超陡亚阈值斜率特性。图1.16是绝缘体-金属相变(Insulator-to-Metal Phase Transition,IMT)材料的工作机理与Hyper-FET的结构示意,Hyper-FET通过在传统MOSFET的源极串联一个由IMT材料构成的非线性电阻实现。当IMT材料两端的电压增大且超过正向转换电压 时,IMT材料由绝缘相转变为金属相,同时由高阻态转变为低阻态,Hyper-FET的导通电流开始急剧增大。类似地,当IMT材料两端的电压减小并低于反向转换电压

时,IMT材料由绝缘相转变为金属相,同时由高阻态转变为低阻态,Hyper-FET的导通电流开始急剧增大。类似地,当IMT材料两端的电压减小并低于反向转换电压 时,IMT材料由金属相转变为绝缘相,同时由低阻态转变为高阻态,Hyper-FET的导通电流开始急剧减小。

时,IMT材料由金属相转变为绝缘相,同时由低阻态转变为高阻态,Hyper-FET的导通电流开始急剧减小。

图1.16 IMT材料工作机理与Hyper-FET的结构示意[23]

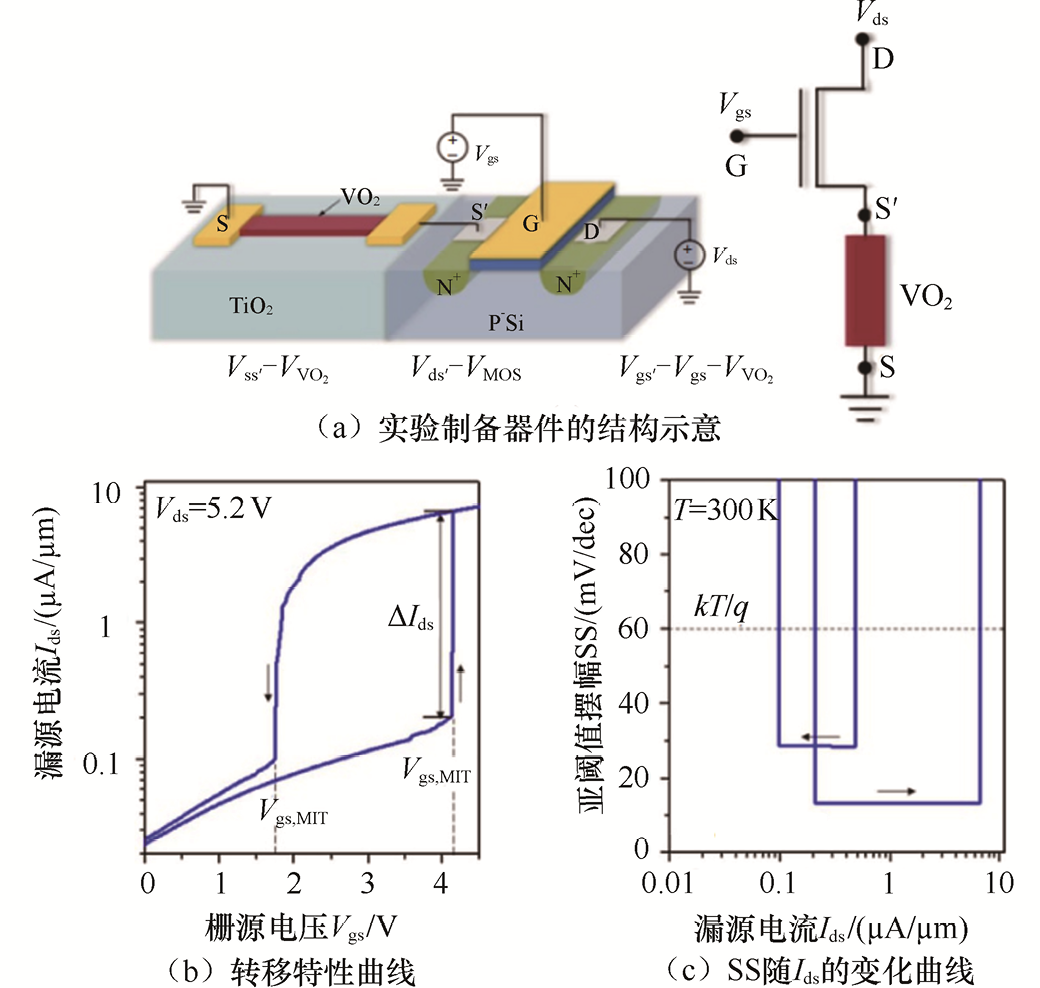

Suman Datta等人也通过实验验证了基于VO2的Hyper-FET具有超陡亚阈值斜率特性[23],VO2是一种IMT材料。实验制备的Hyper-FET由一个硅基N型MOSFET和一个两端VO2器件串联构成,结构及各端口命名如图1.17(a)所示。VO2器件的长度和宽度分别为4 μm和2 μm,器件的薄膜厚度为20 nm。N型MOSFET的栅长和栅宽都是100 μm。图1.17(b)所示为实验测量的Hyper-FET的转移特性曲线,当VO2器件两端的电压达到其转换电压时,VO2发生相变,导致晶体管的导通电流发生急剧变化。图1.17(c)所示为Hyper-FET的SS随 的变化曲线,可以看出,在室温下,Hyper-FET的正向和反向扫描的SSmin < 60 mV/dec,成功突破了玻尔兹曼热力学极限。然而,该器件存在较大的电滞回线窗口,这在实际逻辑计算中是需要避免的。

的变化曲线,可以看出,在室温下,Hyper-FET的正向和反向扫描的SSmin < 60 mV/dec,成功突破了玻尔兹曼热力学极限。然而,该器件存在较大的电滞回线窗口,这在实际逻辑计算中是需要避免的。

图1.17 基于VO2的Hyper-FET实验验证[23]

Hyper-FET利用IMT材料的突变开关特性,能够实现超陡亚阈值斜率特性,因此可将Hyper-FET的结构进一步扩展。本书将把VO2器件串联在基准MOSFET源极、漏极或栅极,以实现超陡亚阈值斜率特性的FET统称为Hyper-FET。Hyper-FET理论上能够实现在多个电流量级范围内的超陡亚阈值斜率特性,并且不会减小基准晶体管的开态电流。然而,目前基于VO2的Hyper-FET仍存在不少技术上的问题。首先,VO2的相变转换电压较高,开态和关态电流比较小,导致实验制备的Hyper-FET存在开启电压较大和超陡亚阈值摆幅电流范围较小的问题。通常,VO2器件转换电压超过1 V,开关比不超过2个电流量级,这限制了Hyper-FET在低压、低功耗设计中的应用[23, 84-85]。其次,转换电压窗口( -

- )决定了Hyper-FET电滞回线窗口的大小,因此减小转换电压窗口也是一个待解决的问题。最后,VO2除了在外加电应力的作用下会产生相变,也容易受环境温度的影响而发生相变[84]。由于Hyper-FET存在上述问题,目前相关研究相对较少,相关应用还处于起步阶段。

)决定了Hyper-FET电滞回线窗口的大小,因此减小转换电压窗口也是一个待解决的问题。最后,VO2除了在外加电应力的作用下会产生相变,也容易受环境温度的影响而发生相变[84]。由于Hyper-FET存在上述问题,目前相关研究相对较少,相关应用还处于起步阶段。

在平板显示和柔性可穿戴电子设备领域,薄膜晶体管(Thin-Film Transistor,TFT)扮演着非常重要的角色。然而随着信息技术的发展和人们生活水平的日益提高,终端设备对TFT的要求也越来越高,例如更高的载流子迁移率、更高的分辨率、更快的响应速度、更高的透明性和更好的伸展性,传统TFT结构和薄膜半导体材料已经无法满足目前的要求,需要进行TFT结构改进或者发展新的薄膜半导体材料[86-87]。非晶硅TFT存在载流子迁移率低(0.5~1 cm2·V-1·s-1)、开关速度慢和稳定性易受光照影响等问题[88]。多晶硅TFT的载流子迁移率较高(大于80 cm2·V-1·s-1),需要采用高温处理工艺和激光退火工艺,且带隙宽度小,这些因素会限制其大面积使用[89-91]。另外,多晶硅TFT的高温(大于450℃)制备工艺和较差的伸展性也限制其在柔性衬底上的应用,晶界的不均匀性还会导致器件间的电学特性差异,如载流子迁移率差异和响应速度差异[92]。在显示器中,每一个像素点都由一个TFT控制,TFT的不均匀性会导致像素点的差异,这对于显示器来说是难以接受的。因此,基于传统硅基TFT的发展已遇到瓶颈,急需寻找新的沟道材料。

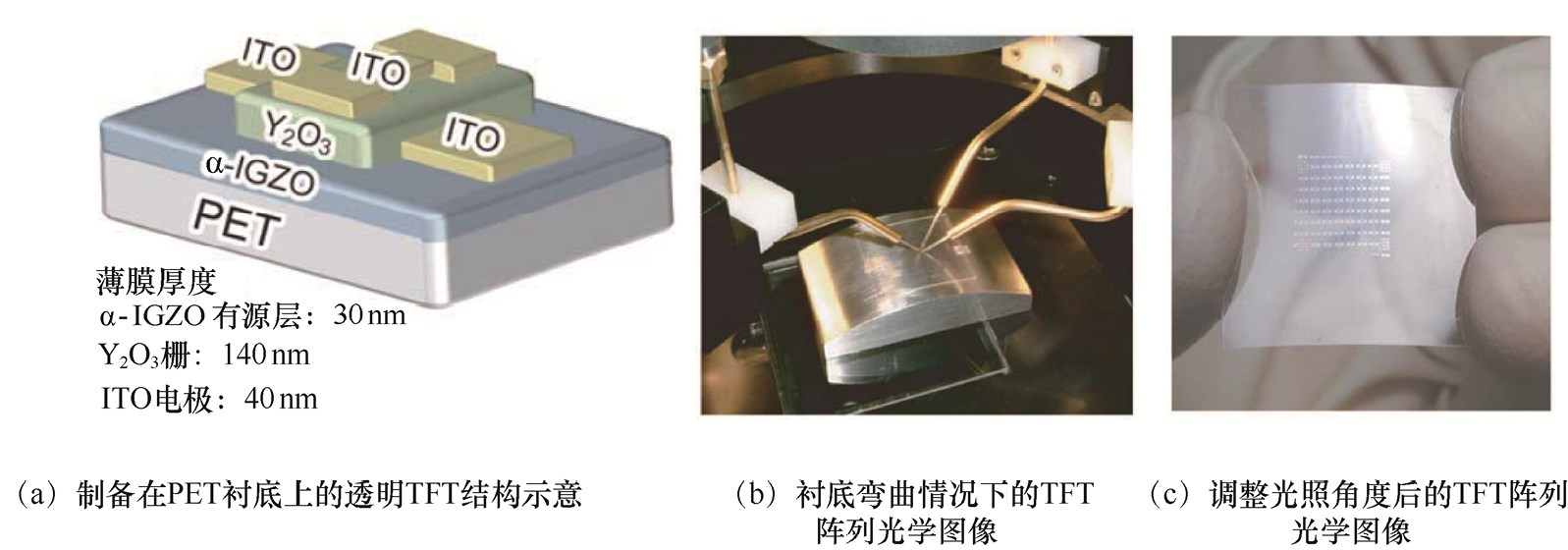

在上述背景下,基于氧化物半导体的TFT脱颖而出,氧化物半导体在平板显示和柔性可穿戴设备领域具有众多优势,如较高载流子迁移率(大于10 cm2·V-1·s-1)、低温制备工艺、高透明性、高均匀性及适用于各种衬底[92-93]。与单晶的金属氧化物半导体相比,非晶氧化物半导体的性质可由沉积的条件、化学配比和组成成分进行调控,使得非晶氧化物半导体的性质具有很高的一致性及可调的光学和电学特性,非常适用于显示领域。目前大多数文献里的非晶氧化物TFT都采用氧化锌基材料作为沟道材料,如铟锌氧化物(Indium-Zinc Oxide,IZO)和铟镓锌氧化物(Indium-Gallium-Zinc Oxide,IGZO)。其中,IGZO-TFT由东京工业大学的Nomura等人于2004年提出[94],图1.18(a)为其结构。该TFT制备在柔性透明PET(Polyethylene Terephthalate)衬底上,具有很高的载流子迁移率和开关比,霍尔迁移率超过10 cm2·V-1·s-1,并且具有可折叠特性,如图1.18(b)和图1.18(c)所示[94]。衬底弯曲情况下,TFT在可见光下完全透明,调整光照角度后,TFT阵列变得可见。由于具有优异的性能和室温制备工艺,IGZO-TFT自提出后便得到了学术界和产业界的广泛关注。2018年,夏普公司发布了应用于大屏幕8 K显示的第五代IGZO-TFT,并且总结了自2012年以来产业界IGZO-TFT的发展历程[95],如图1.19所示。到第五代IGZO-TFT,IGZO显示器分辨率达到8 K,像素点直径小于90 μm。随着大屏幕显示需求的日益增加,IGZO-TFT的集成度和性能将不断提升。

图1.18 柔性透明的IGZO-TFT[94]

图1.19 IGZO-TFT的发展历程[95]

低功耗是物联网技术的核心需求之一,随着物联网技术的发展,应用于柔性可穿戴设备领域的TFT也需要降低自身功耗。但是目前对于低功耗TFT的研究还比较少,对于具有超陡亚阈值斜率特性的氧化物TFT的研究则更为匮乏。一般非晶氧化物TFT为无结型场效应晶体管(Junctionless Field-Effect Transistors,JLT),源极、漏极不需要离子注入和RTA等工艺,氧化物半导体的沉积能在低温甚至室温下完成,所以TFT的制备热预算较低。但是无结型结构导致非晶氧化物TFT不能采用TFET结构来实现超陡亚阈值斜率特性。相对来说,对栅介质做出改变的NC-FET是一种较好的选择[96]。本书第5章尝试通过在TFT的栅叠层中引入具有负电容效应的铪锆氧(HfxZr1-xO2,简称HZO),制备了一种负电容氧化物TFT,实现超陡亚阈值斜率特性,同时增大了TFT的开态电流。

表1.3所示为常见超陡亚阈值斜率晶体管的优缺点。I-MOS由于需要较高的工作电压且难以实现尺寸微缩,无法满足低功耗集成电路和器件的要求;NEM-FET则存在可靠性和转换速度有限的问题。相比之下,TFET、NC-FET和Hyper-FET与传统CMOS工艺兼容性较高,在低功耗集成电路中展现出巨大的应用潜力。然而,在实现产业化之前,这些器件仍面临以下挑战。

(1)TFET的开态电流比传统的MOSFET低2~3个数量级,且超陡亚阈值斜率对应的沟道电流范围较小。实验制备的TFET的I60通常小于1 nA/μm,远未达到实际应用所需的期望值。

(2)NC-FET的栅叠层设计较为复杂。实验制备的NC-FET容易出现电滞回线,导致阈值电压不稳定和工作频率较低。主要原因在于难以在较大的偏置电压和沟道电流范围内实现非线性电容的匹配,以及难以消除铁电材料固有的阻尼效应。

(3)目前Hyper-FET主要基于VO2,但VO2存在热稳定性差、电流开关比低、相变转换电压较高及电滞回线窗口较宽等问题。

表1.3 常见超陡亚阈值斜率晶体管的优缺点

| 器件 |

优势 |

问题 |

|---|---|---|

| MOSFET |

工艺成熟 |

室温下SS极限值是60 mV/dec |

| TFET |

关态电流小,与CMOS工艺兼容性高 |

开态电流小;室温下SS低于60 mV/dec的电流范围小 |

| NC-FET |

开态电流大 |

易出现电滞回线,电容匹配电流范围小 |

| 基于VO2的Hyper-FET |

开态电流大,室温下SS低于60 mV/dec的电流范围大 |

IMT材料热稳定性差,电流开关比低,相变转换电压较高且存在电滞回线窗口 |

| I-MOS |

开态电流大 |

需要较高的工作电压,尺寸难以缩减 |

| NEM-FET |

关态电流小 |

可靠性和良率低,转换速度有限 |

本章介绍了集成电路的发展背景、关键技术挑战及未来发展方向。集成电路作为现代信息产业的基石,其尺寸微缩一直遵循登纳德缩放定律,推动了计算能力和存储密度的持续提升。然而,随着器件尺寸进入深亚微米乃至纳米级别,传统MOSFET面临短沟道效应、寄生电阻、电容效应等诸多问题,使得器件功耗增加,性能提升受到限制。为解决上述问题,学术界和产业界提出了多种改进方案。例如,材料创新(如采用High-K栅介质、金属栅极及高迁移率沟道材料);器件结构优化(如采用FinFET、GAAFET等多栅器件,以增强栅控能力并抑制漏电流)。此外,针对传统MOSFET功耗增加的问题,研究人员提出了超陡亚阈值斜率晶体管,以突破玻尔兹曼热力学极限,实现更低的开关功耗。其中,TFET、NC-FET和Hyper-FET是当前的研究热点,它们分别通过改变载流子输运机制、增强栅控能力或利用IMT材料实现陡峭的开态或关态转换。然而,这些新型器件仍面临诸多挑战(如TFET的小开态电流、NC-FET的电滞回线问题及Hyper-FET的IMT材料稳定性等),距离实际应用还有一段路要走。未来,随着新材料、新结构、新工艺的不断发展,超低功耗器件有望成为集成电路的核心技术。

[1] 张越, 余江, 刘宇, 等. 我国集成电路产业政策协同演变及其有效性研究[J]. 科研管理, 2023, 44(7): 21-31.

[2] SCHALLER R R. Moore’s law: past, present and future[J]. IEEE Spectrum, 1997, 34(6): 52-59.

[3] SARAH RAVI. ITRS 2015 Executive Report[EB/OL].(2015-06-06)[2025-03-27].

[4] PACKAN P, AKBAR S, ARMSTRONG M, et al. High performance 32nm logic technology featuring 2nd generation high-k metal gate transistors[C]// IEEE International Electron Devices Meeting. Baltimore, MD, USA. IEEE, 2009: 1-4.

[5] LEE B H, OH J, TSENG H H, et al. Gate stack technology for nanoscale devices[J]. Materials Today, 2006, 9(6): 32-40.

[6] MISTRY K, ALLEN C, AUTH C, et al. A 45nm logic technology with high-k metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging[C]// IEEE International Electron Devices Meeting. Washington, DC, USA. IEEE, 2007: 247-250.

[7] WILK G D, WALLACE R M, ANTHONY J M. High-κ gate dielectrics: current status and materials properties considerations[J]. Journal of Applied Physics, 2001, 89(10): 5243-5275.

[8] LEE M L, FITZGERALD E A, BULSARA M T, et al. Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors[J]. Journal of Applied Physics, 2005, 97(1): 011101.

[9] SIMOEN E, MITARD J, HELLINGS G, et al. Challenges and opportunities in advanced Ge pMOSFETs[J]. Materials Science in Semiconductor Processing, 2012, 15(6): 588-600.

[10] KIM S H, YOKOYAMA M, TAOKA N, et al. Enhancement technologies and physical understanding of electron mobility in Ⅲ-Ⅴ n-MOSFETs with strain and MOS interface buffer engineering[C]// International Electron Devices Meeting. Washington, DC, USA. IEEE, 2011: 13.4.1-13.4.4.

[11] FRANK D J, DENNARD R H, NOWAK E, et al. Device scaling limits of Si MOSFETs and their application dependencies[J]. Proceedings of the IEEE, 2001, 89(3): 259-288.

[12] SZE S M, NG K K. Physics of Semiconductor Devices[M]. New York: Wiley, 2007.

[13] CHAUDHRY A, KUMAR M J. Controlling short-channel effects in deep-submicron SOI MOSFETs for improved reliability: a review[J]. IEEE Transactions on Device and Materials Reliability, 2004, 4(1): 99-109.

[14] HISAMOTO D, LEE W C, KEDZIERSKI J, et al. FinFET-a self-aligned double-gate MOSFET scalable to 20 nm[J]. IEEE Transactions on Electron Devices, 2000, 47(12): 2320-2325.

[15] YU B, CHANG L, AHMED S, et al. FinFET scaling to 10 nm gate length[C]//Digest. International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2002: 251-254.

[16] COLINGE J P. FinFETs and other multi-gate transistors[M]. Cham: Springer, 2008.

[17] CHEN A. Emerging research device roadmap and perspectives[C]// IEEE International Conference on IC Design & Technology. Austin, TX, USA. IEEE, 2014: 1-4.

[18] HAENSCH W, NOWAK E J, DENNARD R H, et al. Silicon CMOS devices beyond scaling[J]. IBM Journal of Research and Development, 2006, 50(4.5): 339-361.

[19] IONESCU A M, RIEL H. Tunnel field-effect transistors as energy-efficient electronic switches[J]. Nature, 2011, 479(7373): 329-337.

[20] SALAHUDDIN S, DATTA S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices[J]. Nano Letters, 2008, 8(2): 405-410.

[21] AKARVARDAR K, ELATA D, PARSA R, et al. Design considerations for complementary nanoelectromechanical logic gates[C]// IEEE International Electron Devices Meeting. Washington, DC, USA. IEEE, 2007: 299-302.

[22] CHOI W Y, SONG J Y, LEE J D, et al. A novel biasing scheme for I-MOS (impact-ionization MOS) devices[J]. IEEE Transactions on Nanotechnology, 2005, 4(3): 322-325.

[23] SHUKLA N, THATHACHARY A V, AGRAWAL A, et al. A steep-slope transistor based on abrupt electronic phase transition[J]. Nature Communications, 2015, 6: 7812.

[24] SEABAUGH A, ALESSANDRI C, HEIDARLOU M A, et al. Steep slope transistors: tunnel FETs and beyond[C]// 46th European Solid-State Device Research Conference. Lausanne, Switzerland. IEEE, 2016: 349-351.

[25] 张新征. 集成电路发展模式的演进透视——以美国DARPA电子复兴计划为视角[J]. 军事文摘, 2019(21): 54-57.

[26] EDGAR L J. Method and apparatus for controlling electric currents: US Patent 1,745,175[P]. 1930-1-28.

[27] RIORDAN M, HODDESON L, HERRING C. Invention of the transistor[J]. American Physical Society, 1999.

[28] KAHNG D. Silicon-silicon dioxide field induced surface devices[C]//IRE Solid State Device Res. Conf, 1960.

[29] WANLASS F M. Low stand-by power complementary field effect circuitry: US Patent 3,356,858[P]. 1967-12-5.

[30] NEAMEN D A, BISWAS D. Semiconductor physics and devices[M]. New York: Mcgraw-Hill Higher Education, 2011.

[31] ITRS 2013 Executive Summary.

[32] LO S H, BUCHANAN D A, TAUR Y, et al. Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thin-oxide nMOSFET’s[J]. IEEE Electron Device Letters, 1997, 18(5): 209-211.

[33] CHANG L, YANG K J, YEO Y C, et al. Direct-tunneling gate leakage current in double-gate and ultrathin body MOSFETs[J]. IEEE Transactions on Electron Devices, 2002, 49(12): 2288-2295.

[34] LO S H, BUCHANAN D A, TAUR Y. Modeling and characterization of quantization, polysilicon depletion, and direct tunneling effects in MOSFETs with ultrathin oxides[J]. IBM Journal of Research and Development, 1999, 43(3): 327-337.

[35] HUANG C L, ARORA N D. Measurements and modeling of MOSFET I-V characteristics with polysilicon depletion effect[J]. IEEE Transactions on Electron Devices, 2002, 40(12): 2330-2337.

[36] BARNES J J, SHIMOHIGASHI K, DUTTON R W. Short-channel MOSFETs in the punchthrough current mode[J]. IEEE Journal of Solid-State Circuits, 1979, 14(2): 368-375.

[37] KOTANI N, KAWAZU S. Computer analysis of punch-through in MOSFETs[J]. Solid-State Electronics, 1979, 22(1): 63-70.

[38] VEENDRICK H J M. Short-circuit dissipation of static CMOS circuitry and its impact on the design of buffer circuits[J]. IEEE Journal of Solid-State Circuits, 1984, 19(4): 468-473.

[39] DORIS B, IEONG M, KANARSKY T, et al. Extreme scaling with ultra-thin Si channel MOSFETs[C]//Digest. International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2002: 267-270.

[40] TENBROEK B M, LEE M S L, REDMAN-WHITE W, et al. Self-heating effects in SOI MOSFETs and their measurement by small signal conductance techniques[J]. IEEE Transactions on Electron Devices, 1996, 43(12): 2240-2248.

[41] JIANG H, LIU X Y, XU N, et al. Investigation of self-heating effect on hot carrier degradation in multiple-fin SOI FinFETs[J]. IEEE Electron Device Letters, 2015, 36(12): 1258-1260.

[42] CROS A, ROMANJEK K, FLEURY D, et al. Unexpected mobility degradation for very short devices: a new challenge for CMOS scaling[C]// International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2006: 1-4.

[43] RIM K, NARASIMHA S, LONGSTREET M, et al. Low field mobility characteristics of sub-100nm unstrained and strained Si MOSFETs[C]//Digest. International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2002: 43-46.

[44] DATTA S. Recent advances in high performance CMOS transistors: from planar to non-planar[J]. Interface Magazine, 2013, 22(1): 41-46.

[45] PASSLACK M, ZURCHER P, RAJAGOPALAN K, et al. High mobility III-V MOSFETs for RF and digital applications[C]//2007 IEEE International Electron Devices Meeting. Washington, DC, USA. IEEE, 2007: 621-624.

[46] KIM S, KONAR A, HWANG W S, et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals[J]. Nature Communications, 2012, 3(1): 1011.

[47] SWAMINATHAN K, KULTURSAY E, SARIPALLI V, et al. Steep-slope devices: from dark to dim silicon[J]. IEEE Micro, 2013, 33(5): 50-59.

[48] WU S Y. A new ferroelectric memory device, metal-ferroelectric-semiconductor transistor[J]. IEEE Transactions on Electron Devices, 1974, 21(8): 499-504.

[49] JANA R K, SNIDER G L, JENA D. On the possibility of sub 60 mV/decade subthreshold switching in piezoelectric gate barrier transistors[J]. Physica Status Solidi C, 2013, 10(11): 1469-1472.

[50] SEABAUGH A C, ZHANG Q. Low-voltage tunnel transistors for beyond CMOS logic[J]. Proceedings of the IEEE, 2010, 98(12): 2095-2110.

[51] NAZIR G, REHMAN A, PARK S J. Energy-efficient tunneling field-effect transistors for low-power device applications: challenges and opportunities[J]. ACS Applied Materials & Interfaces, 2020, 12(42): 47127-47163.

[52] KANE E O. Zener tunneling in semiconductors[J]. Journal of Physics and Chemistry of Solids, 1960, 12(2): 181-188.

[53] VANDENBERGHE W G, VERHULST A S, GROESENEKEN G, et al. Analytical model for a tunnel field-effect transistor[C]// 14th IEEE Mediterranean Electrotechnical Conference. Ajaccio, France. IEEE, 2008: 923-928.

[54] KAO K H, VERHULST A S, VANDENBERGHE W G, et al. Direct and indirect band-to-band tunneling in germanium-based TFETs[J]. IEEE Transactions on Electron Devices, 2011, 59(2): 292-301.

[55] GLASS S, VON DEN DRIESCH N, STRANGIO S, et al. Experimental examination of tunneling paths in SiGe/Si gate-normal tunneling field-effect transistors[J]. Applied Physics Letters, 2017, 111(26): 263504.

[56] ROSCA T, SAEIDI A, MEMISEVIC E, et al. An experimental study of heterostructure tunnel FET nanowire arrays: digital and analog figures of merit from 300K to 10K[C]// IEEE International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2018: 13.5.1-13.5.4.

[57] SARKAR D, XIE X J, LIU W, et al. A subthermionic tunnel field-effect transistor with an atomically thin channel[J]. Nature, 2015, 526(7571): 91-95.

[58] HU C M, CHOU D, PATEL P, et al. Green transistor - a VDD scaling path for future low power ICs[C]// International Symposium on VLSI Technology, Systems and Applications. Hsinchu, Taiwan, China. IEEE, 2008: 14-15.

[59] BLAESER S, GLASS S, SCHULTE-BRAUCKS C, et al. Line tunneling dominating charge transport in SiGe/Si heterostructure TFETs[J]. IEEE Transactions on Electron Devices, 2016, 63(11): 4173-4178.

[60] HUANG Q Q, ZHAN Z, HUANG R, et al. Self-depleted T-gate Schottky barrier tunneling FET with low average subthreshold slope and high ION/IOFF by gate configuration and barrier modulation[C]//2011 International Electron Devices Meeting. Washington, DC. IEEE, 2011: 16.2.1-16.2.4.

[61] HUANG Q Q, HUANG R, ZHAN Z, et al. A novel Si tunnel FET with 36mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration[C]//2012 International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2012: 8.5.1-8.5.4.

[62] ROOYACKERS R, VANDOOREN A, VERHULST A S, et al. Ge-source vertical tunnel FETs using a novel replacement-source integration scheme[J]. IEEE Transactions on Electron Devices, 2014, 61(12): 4032-4039.

[63] LEE M H, WEI Y T, CHU K Y, et al. Steep slope and near non-hysteresis of FETs with antiferroelectric-like HfZrO for low-power electronics[J]. IEEE Electron Device Letters, 2015, 36(4): 294-296.

[64] KARDA K, JAIN A, MOULI C, et al. An anti-ferroelectric gated Landau transistor to achieve sub-60 mV/dec switching at low voltage and high speed[J]. Applied Physics Letters, 2015, 106(16): 163501.

[65] LANDAU L D, KHALATNIKOV I M. On the anomalous absorption of sound near a second order phase transition point[C]//Dokl. Akad. Nauk SSSR. 1954, 96(469): 25.

[66] KHAN A I, BHOWMIK D, YU P, et al. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures[J]. Applied Physics Letters, 2011, 99(11): 113501.

[67] APPLEBY D J R, PONON N K, KWA K S K, et al. Experimental observation of negative capacitance in ferroelectrics at room temperature[J]. Nano Letters, 2014, 14(7): 3864-3868.

[68] KHAN A I, CHATTERJEE K, WANG B, et al. Negative capacitance in a ferroelectric capacitor[J]. Nature Materials, 2015, 14(2): 182-186.

[69] KU H, SHIN C. Transient response of negative capacitance in P(VDF0.75-TrFE0.25) organic ferroelectric capacitor[J]. IEEE Journal of the Electron Devices Society, 2017, 5(3): 232-236.

[70] HOFFMANN M, PEŠIĆ M, CHATTERJEE K, et al. Direct observation of negative capacitance in polycrystalline ferroelectric HfO2[J]. Advanced Functional Materials, 2016, 26(47): 8643-8649.

[71] SALVATORE G A, RUSU A, IONESCU A M. Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor[J]. Applied Physics Letters, 2012, 100(16): 163504.

[72] RUSU A, SALVATORE G A, JIMÉNEZ D, et al. Metal-Ferroelectric-Meta-Oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification[C]//2010 International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2010: 16.3.1-16.3.4.

[73] JO J, SHIN C. Impact of temperature on negative capacitance field-effect transistor[J]. Electronics Letters, 2015, 51(1): 106-108.

[74] SALVATORE G A, BOUVET D, IONESCU A M. Demonstration of subthrehold swing smaller than 60mV/decade in Fe-FET with P(VDF-TrFE)/SiO2 gate stack[C]//2008 IEEE International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2008: 1-4.

[75] DASGUPTA S, RAJASHEKHAR A, MAJUMDAR K, et al. Sub-kT/q switching in strong inversion in PbZr0.52Ti0.48O3 gated negative capacitance FETs[J]. IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, 2015, 1: 43-48.

[76] LEE M H, FAN S T, TANG C H, et al. Physical thickness 1.x nm ferroelectric HfZrOx negative capacitance FETs[C]// IEEE International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2016: 12.1.1-12.1.4.

[77] SINGH P, SINGH R K, SINGH B R. An approach to enhance memory retention capacity in MFIS structures using different insulating buffer layer[J]. Ferroelectrics, 2017, 519(1): 213-222.

[78] FRANK D J, SOLOMON P M, DUBOURDIEU C, et al. The quantum metal ferroelectric field-effect transistor[J]. IEEE Transactions on Electron Devices, 2014, 61(6): 2145-2153.

[79] KHAN A I, RADHAKRISHNA U, CHATTERJEE K, et al. Negative capacitance behavior in a leaky ferroelectric[J]. IEEE Transactions on Electron Devices, 2016, 63(11): 4416-4422.

[80] KAHNG D, SZE S M. A floating gate and its application to memory devices[J]. The Bell System Technical Journal, 1967, 46(6): 1288-1295.

[81] ZHOU J R, HAN G Q, LI Q L, et al. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with Sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved Ids[C]//2016 IEEE International Electron Devices Meeting. San Francisco, CA, USA. IEEE, 2016: 12.2.1-12.2.4.

[82] ZHOU J R, HAN G Q, PENG Y, et al. Ferroelectric negative capacitance GeSn PFETs with sub-20 mV/decade subthreshold swing[J]. IEEE Electron Device Letters, 2017, 38(8): 1157-1160.

[83] PAHWA G, DUTTA T, AGARWAL A, et al. Analysis and compact modeling of negative capacitance transistor with high ON-current and negative output differential resistance: part I: model description[J]. IEEE Transactions on Electron Devices, 2016, 63(12): 4981-4985.

[84] FROUGIER J, SHUKLA N, DENG D, et al. Phase-Transition-FET exhibiting steep switching slope of 8mV/decade and 36% enhanced ON current[C]//2016 IEEE Symposium on VLSI Technology. Honolulu, HI, USA. IEEE, 2016: 1-2.

[85] VERMA A, SONG B, MEYER D, et al. Demonstration of GaN HyperFETs with ALD VO2[C]// 74th Annual Device Research Conference. Newark, DE, USA. IEEE, 2016: 1-2.

[86] JENIFER K, ARULKUMAR S, PARTHIBAN S, et al. A review on the recent advancements in tin oxide-based thin-film transistors for large-area electronics[J]. Journal of Electronic Materials, 2020, 49(12): 7098-7111.

[87] LEE S Y. Comprehensive review on amorphous oxide semiconductor thin film transistor[J]. Transactions on Electrical and Electronic Materials, 2020, 21(3): 235-248.

[88] FLEWITT A J. Hydrogenated amorphous silicon thin-film transistors (a-Si:H TFTs)[J]. Handbook of Visual display Technology, 2016: 887-909.

[89] JEONG J K. The status and perspectives of metal oxide thin-film transistors for active matrix flexible displays[J]. Semiconductor Science and Technology, 2011, 26(3): 034008.

[90] SHENG J Z, JEONG H J, HAN K L, et al. Review of recent advances in flexible oxide semiconductor thin-film transistors[J]. Journal of Information Display, 2017, 18(4): 159-172.

[91] MATSUO N, HEYA A, HAMADA H. Review: technology trends of poly-Si TFTs from the viewpoints of crystallization and device performance[J]. ECS Journal of Solid State Science and Technology, 2019, 8(4): P239-P252.

[92] FORTUNATO E, BARQUINHA P, MARTINS R. Oxide semiconductor thin-film transistors: a review of recent advances[J]. Advanced Materials, 2012, 24(22): 2945-2986.

[93] ZHANG Y H, MEI Z X, LIANG H L, et al. Review of flexible and transparent thin-film transistors based on zinc oxide and related materials[J]. Chinese Physics B, 2017, 26(4): 047307.

[94] NOMURA K, OHTA H, TAKAGI A, et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors[J]. Nature, 2004, 432(7016): 488-492.

[95] HARA Y, KIKUCHI T, KITAGAWA H, et al. IGZO-TFT technology for large-screen 8K display[J]. Journal of the Society for Information Display, 2018, 26(3): 169-177.

[96] LI Y X, LIANG R R, WANG J B, et al. Negative capacitance oxide thin-film transistor with sub-60 mV/decade subthreshold swing[J]. IEEE Electron Device Letters, 2019, 40(5): 826-829.